## **CMOS** Image Sensors

Online at: https://doi.org/10.1088/978-0-7503-3235-4

## **CMOS Image Sensors**

#### Konstantin D Stefanov

Centre for Electronic Imaging, The Open University, Milton Keynes, UK

**IOP** Publishing, Bristol, UK

© IOP Publishing Ltd 2022

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the publisher, or as expressly permitted by law or under terms agreed with the appropriate rights organization. Multiple copying is permitted in accordance with the terms of licences issued by the Copyright Licensing Agency, the Copyright Clearance Centre and other reproduction rights organizations.

Permission to make use of IOP Publishing content other than as set out above may be sought at permissions@ioppublishing.org.

Konstantin D Stefanov has asserted their right to be identified as the author of this work in accordance with sections 77 and 78 of the Copyright, Designs and Patents Act 1988.

ISBN978-0-7503-3235-4 (ebook)ISBN978-0-7503-3233-0 (print)ISBN978-0-7503-3236-1 (myPrint)ISBN978-0-7503-3234-7 (mobi)

DOI 10.1088/978-0-7503-3235-4

Version: 20221101

IOP ebooks

British Library Cataloguing-in-Publication Data: A catalogue record for this book is available from the British Library.

Published by IOP Publishing, wholly owned by The Institute of Physics, London

IOP Publishing, No.2 The Distillery, Glassfields, Avon Street, Bristol, BS2 0GR, UK

US Office: IOP Publishing, Inc., 190 North Independence Mall West, Suite 601, Philadelphia, PA 19106, USA

To David Burt, from whom I have learnt many of the things in this book, and to my family, for their support and encouragement.

## Contents

| Preface<br>Acknowledgement<br>Author biography |                                                           | xi   |

|------------------------------------------------|-----------------------------------------------------------|------|

|                                                |                                                           | xiii |

|                                                |                                                           | xiv  |

| List                                           | of frequently used abbreviations                          | XV   |

|                                                | le of common symbols and units                            | xvi  |

| 1                                              | The fundamentals                                          | 1-1  |

| 1.1                                            | Introduction—what is an image sensor and what does it do? | 1-1  |

| 1.2                                            | Charge generation                                         | 1-2  |

|                                                | 1.2.1 Photoeffect                                         | 1-2  |

|                                                | 1.2.2 Ionisation                                          | 1-7  |

| 1.3                                            | Charge collection                                         | 1-9  |

|                                                | 1.3.1 Carrier lifetime                                    | 1-10 |

|                                                | 1.3.2 Recombination                                       | 1-12 |

|                                                | 1.3.3 Drift                                               | 1-14 |

|                                                | 1.3.4 Diffusion                                           | 1-17 |

| 1.4                                            | Charge transfer                                           | 1-19 |

| 1.5                                            | Charge conversion                                         | 1-20 |

| 1.6                                            | pn junction                                               | 1-22 |

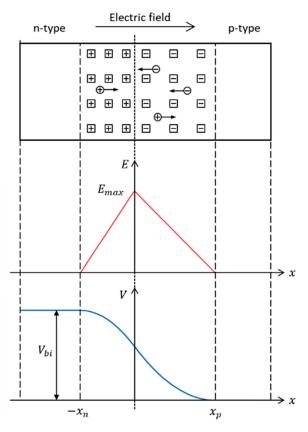

|                                                | 1.6.1 <i>pn</i> junction in equilibrium                   | 1-22 |

|                                                | 1.6.2 pn junction under reverse bias                      | 1-26 |

|                                                | 1.6.3 Charge collection                                   | 1-29 |

|                                                | 1.6.4 Junction capacitance                                | 1-32 |

| 1.7                                            | MOS capacitor                                             | 1-33 |

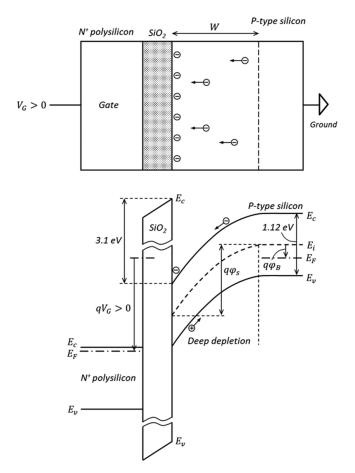

|                                                | 1.7.1 Depletion                                           | 1-33 |

|                                                | 1.7.2 Gate capacitance                                    | 1-37 |

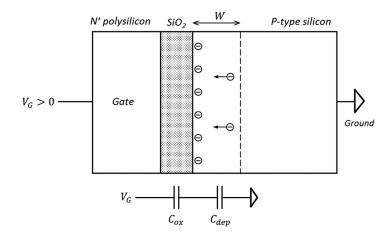

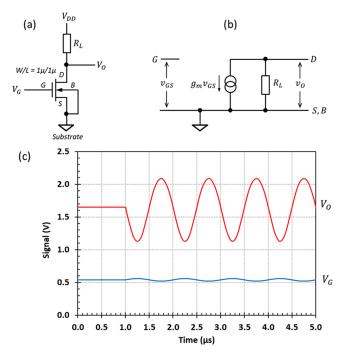

| 1.8                                            | MOS transistor                                            | 1-38 |

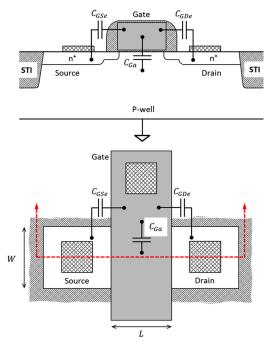

|                                                | 1.8.1 Structure                                           | 1-38 |

|                                                | 1.8.2 MOSFET characteristics                              | 1-40 |

|                                                | 1.8.3 Output resistance and body effect                   | 1-44 |

|                                                | 1.8.4 Transistor threshold                                | 1-47 |

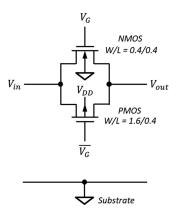

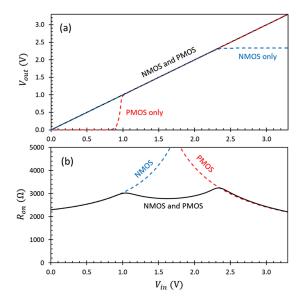

|                                                | 1.8.5 Analogue switch                                     | 1-51 |

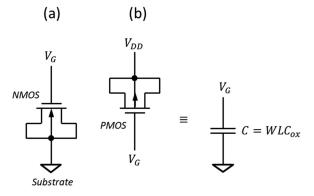

|                                                | 1.8.6 MOSFET capacitor                                    | 1-53 |

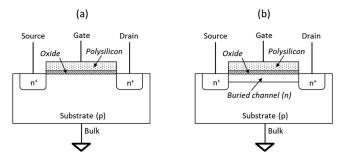

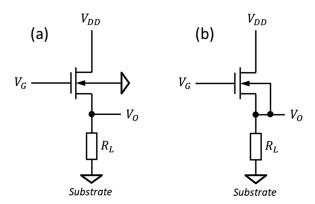

| 1.9                                            | Source follower                                           | 1-54 |

|                                                | 1.9.1 Gain                                                | 1-54 |

|     | 1.9.2 Input capacitance                     | 1-58 |

|-----|---------------------------------------------|------|

|     | Chapter summary                             | 1-60 |

|     | References                                  | 1-61 |

| 2   | CMOS pixel architectures                    | 2-1  |

| 2.1 | History and technology                      | 2-1  |

| 2.2 | Photodiode APS                              | 2-2  |

|     | 2.2.1 Structure                             | 2-2  |

|     | 2.2.2 Operation                             | 2-5  |

|     | 2.2.3 Performance                           | 2-9  |

| 2.3 | Pinned photodiode (4T)                      | 2-11 |

|     | 2.3.1 Structure                             | 2-11 |

|     | 2.3.2 Operation                             | 2-15 |

|     | 2.3.3 Charge storage and full well capacity | 2-17 |

|     | 2.3.4 Charge transfer                       | 2-22 |

|     | 2.3.5 Image lag                             | 2-27 |

|     | 2.3.6 Transistor sharing                    | 2-33 |

| 2.4 | Other PPD-based pixels                      | 2-33 |

|     | 2.4.1 Global reset (5T)                     | 2-33 |

|     | 2.4.2 In-pixel signal storage               | 2-35 |

|     | 2.4.3 High dynamic range                    | 2-37 |

| 2.5 | Hybrid and 3D image sensors                 | 2-41 |

|     | Chapter summary                             | 2-43 |

|     | References                                  | 2-44 |

| 3   | Advanced image sensor topics                | 3-1  |

| 3.1 | Photocurrent                                | 3-1  |

| 3.2 | Dark current                                | 3-6  |

|     | 3.2.1 Sources of dark current               | 3-6  |

|     | 3.2.2 Depletion dark current                | 3-9  |

|     | 3.2.3 Diffusion dark current                | 3-12 |

|     | 3.2.4 Surface dark current                  | 3-15 |

|     | 3.2.5 Dark current suppression by pinning   | 3-16 |

|     | 3.2.6 Temperature for dark current doubling | 3-17 |

| 3.3 | Reflective barrier                          | 3-18 |

| 3.4 | Back-side illumination                      | 3-21 |

|     | 3.4.1 Front and back-side illumination      | 3-21 |

|     | 3.4.2 Back-side interface                   | 3-24 |

|     | 3.4.3 BSI technologies                         | 3-28 |

|-----|------------------------------------------------|------|

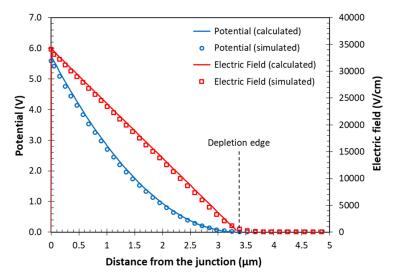

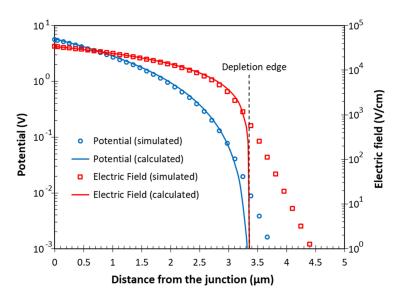

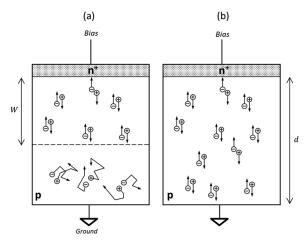

| 3.5 | Depletion depth and potential gradients        | 3-29 |

|     | 3.5.1 Depletion depth as a 3D effect           | 3-29 |

|     | 3.5.2 Potential gradients in PPDs              | 3-31 |

| 3.6 | Punch-through                                  | 3-31 |

| 3.7 | Field-induced junctions                        | 3-35 |

|     | Chapter summary                                | 3-36 |

|     | References                                     | 3-37 |

| 4   | Noise and readout techniques                   | 4-1  |

| 4.1 | Noise in image sensors                         | 4-1  |

|     | 4.1.1 Thermal and reset noise                  | 4-1  |

|     | 4.1.2 Shot noise                               | 4-6  |

|     | 4.1.3 1/f and random telegraph noise           | 4-8  |

|     | 4.1.4 MOSFET noise                             | 4-10 |

|     | 4.1.5 Source follower noise                    | 4-12 |

| 4.2 | Correlated double sampling                     | 4-14 |

|     | 4.2.1 Reset noise suppression                  | 4-14 |

|     | 4.2.2 Double sampling                          | 4-15 |

|     | 4.2.3 Dual slope integrator                    | 4-19 |

|     | 4.2.4 Optimal signal processing                | 4-22 |

|     | 4.2.5 Digital CDS and multiple sampling        | 4-24 |

|     | 4.2.6 Column-level noise                       | 4-28 |

|     | 4.2.7 MOSFET optimisation                      | 4-32 |

|     | Chapter summary                                | 4-33 |

|     | References                                     | 4-34 |

| 5   | Characterisation                               | 5-1  |

| 5.1 | Introduction                                   | 5-1  |

| 5.2 | Readout modes                                  | 5-2  |

| 5.3 | Principles of EO characterisation              | 5-4  |

| 5.4 | Photoresponse, non-uniformity and nonlinearity | 5-7  |

| 5.5 | Photon transfer curve                          | 5-17 |

|     | 5.5.1 Principles                               | 5-17 |

|     | 5.5.2 Frame differencing                       | 5-21 |

|     | 5.5.3 System gain, CVF and noise               | 5-24 |

|     | 5.5.4 Nonlinear PTC                            | 5-27 |

|     | 5.5.5 PTC from dark current                    | 5-30 |

|      | 5.5.6 Practical tips for the PTC         | 5-31 |

|------|------------------------------------------|------|

|      | 5.5.7 The PTC as a diagnostic tool       | 5-34 |

| 5.6  | X-ray calibration                        | 5-36 |

| 5.7  | Full well capacity and dynamic range     | 5-39 |

| 5.8  | Dark current and DSNU                    | 5-41 |

| 5.9  | Noise measurement                        | 5-44 |

| 5.10 | Image lag                                | 5-48 |

| 5.11 | Quantum efficiency                       | 5-50 |

|      | 5.11.1 Principles                        | 5-50 |

|      | 5.11.2 Pain–Hancock method               | 5-54 |

|      | 5.11.3 Modulation transfer function      | 5-57 |

| 5.12 | Electrical transfer function             | 5-62 |

|      | Chapter summary                          | 5-65 |

|      | References                               | 5-66 |

| 6    | Electronics                              | 6-1  |

| 6.1  | On-chip electronics                      | 6-1  |

|      | 6.1.1 Architecture                       | 6-1  |

|      | 6.1.2 Column buffers                     | 6-2  |

|      | 6.1.3 Column amplifiers                  | 6-3  |

|      | 6.1.4 CDS circuits                       | 6-7  |

|      | 6.1.5 Row drivers                        | 6-12 |

|      | 6.1.6 Pixel addressing                   | 6-14 |

|      | 6.1.7 Analogue switches and multiplexers | 6-17 |

|      | 6.1.8 Output amplifier                   | 6-19 |

| 6.2  | Off-chip electronics                     | 6-21 |

|      | 6.2.1 General requirements               | 6-21 |

|      | 6.2.2 Signal amplifiers                  | 6-23 |

|      | 6.2.3 Power supplies                     | 6-29 |

|      | 6.2.4 Bias circuits                      | 6-30 |

|      | 6.2.5 Noise measurements                 | 6-32 |

|      | Chapter summary                          | 6-34 |

|      | References                               | 6-35 |

## Preface

Image sensors are fascinating devices that straddle the boundary between semiconductor physics and electronic engineering. Nowadays, they are used in almost everything, come in bewildering varieties, and are mostly made with complementary metal-oxide semiconductor (CMOS) technology, like the billions of other integrated circuits (IC) manufactured every year. And they look good! They are among the handful of IC types which can be easily seen through their transparent glass cover.

To understand how they work, we need to know a fair bit of semiconductor physics, especially when dealing with high performance imagers designed for science applications. However, this is not always enough; there are a lot of electronic circuits inside a CMOS image sensor (CIS), and even the simple ones can show subtle behaviour and throw up surprises. Without claiming to cover everything, this book strives to cover both the semiconductor physics and the essential electronics found inside a CMOS image sensor.

A relatively small number of concepts from semiconductor physics form the backbone of image sensors' operation—depletion, drift, diffusion, recombination, charge conversion, to name a few. Knowing them well provides the foundations to understand practically all image sensors and helps with the more complex structures that exist or are yet to be invented.

It is impossible to imagine doing any serious work into image sensors without semiconductor technology CAD (TCAD). Very often it is the only way to 'see' what is happening inside, and this book offers many examples of device simulations. A successful TCAD simulation is a good result, but does not guarantee that something will work. However, if something doesn't work in TCAD, it's probably not going to work in silicon either.

To make full use of this book, some basic knowledge of electronics is essential. Knowing what an amplifier is, being familiar with gain, bandwidth, and noise, can be very advantageous. Freely available electronic simulation tools, such as SPICE, are great for designing and verifying the performance of various circuits. Throughout my career, my hobby in electronics has helped me enormously when working with image sensors. Building my first electronic circuit at around 14 years of age, I was fascinated but I only had a faint understanding of how it worked. In a few years, electronics gradually started to make more sense, and after learning semiconductor physics at university it was clear to me that this is what I wanted to do.

I have often found that many important 'bread and butter' topics in image sensors and their operation are difficult to find in books and papers, and sometimes are not there at all. Some of those I have only been able to find out in discussions with more experienced colleagues who have been longer in the field. This book is an attempt to put some of this 'unofficial knowledge', some of which could be simply due to my ignorance, in one place.

This book is intended to be used as a tutorial and has many examples, taken mostly from practice. Solved examples are essential for proper understanding of the theory and bring 'life' to the formulas. They also help with appreciating the parameters in real-world applications. Very often, a good enough grasp of the phenomena can be obtained from relatively simple formulas. They may not be super-accurate, but can give a decent approximate answer and can serve as a 'sanity check' for more detailed results derived from TCAD and SPICE.

Some of the contents of this book are derived from a practical course on CMOS image sensor operation and characterisation techniques that we deliver at the Open University to students and staff.

Chapter 1 covers the fundamentals of image sensors, starting with the photoeffect and charge generation, and including charge collection and transfer, drift and diffusion, recombination, and carrier lifetime. The chapter also describes the fundamental building blocks of CIS—diodes, MOS capacitors and transistors, and the basic MOSFET circuits—source followers and analogue switches.

Chapter 2 deals with 3T, 4T and other CMOS pixel architectures. Most of the material in this chapter is dedicated to the pinned photodiode (PPD) because of its importance for image sensor technology. This includes the operating principles of the PPD, doping profiles, charge transfer, full well capacity and image lag. Other PPD-based designs, such as the 5T, pixels with charge domain signal storage, and several high dynamic range pixels are also covered, as well as hybrid and 3D-intgerated sensors.

In chapter 3, some of the more specialised subjects in CIS performance are discussed, such as the collection of photogenerated signal in pn junctions, the sources of dark current, reflective barriers, the backside interface and its effect on the quantum efficiency in backside-illuminated sensors, potential gradients and punch-through.

Chapter 4 is dedicated to the different sources of noise in electronics components and MOSFETs, the readout techniques used for CIS and their noise performance. The two main correlated double sampling (CDS) methods, based on the double sampling and the dual slope integrator are discussed in detail and their noise performance is compared. In addition, the chapter deals with digital CDS, noise in the column readout in CIS, and MOSET noise optimisation.

Chapter 5 begins with the principles of electro-optical characterisation and readout modes in CIS. It describes the measurement methods for obtaining the most important sensor parameters: photoresponse, linearity, system gain, readout noise, dynamic range, full well capacity, dark current, image lag, quantum efficiency and modulation transfer function. Special attention is paid to the photon transfer curve (PTC) because of the wealth of information it provides, and many experimental tips are given.

Chapter 6 covers the on-chip and off-chip electronics used to control and readout the pixels and the sensor. On-chip amplifiers, correlated double sampling circuits, buffers, switches, drivers and logic are some of the circuits described here. Off-chip electronics providing power, bias and amplification is shown with practical examples and performance calculations.

I hope that this book will be useful to all who are using, characterising, or designing CMOS image sensors, beginners and experts alike.

## Acknowledgement

The stimulating research environment at the Centre for Electronic Imaging (CEI) at the Open University is one of the main reasons for the existence of this book. Many of the topics and ideas presented here came up from discussions with my colleagues, students, industrial collaborators, and external partners, and by the challenges and the difficult questions they often had.

I am grateful for the inspiration and the knowledge I have gained thanks to David Burt, Andrew Holland, Chris Damerell, Ray Bell, Jérôme Pratlong, Paul Jerram, Doug Jordan, Neil Murray, Pete Turner, Dave Barry, David Hall, Matthew Soman, Julian Heymes, Martin Prest, James Ivory, Chiaki Crews, Nathan Bush, Steve Bowring and Giulio Villani.

Finally, I would like to thank IOP Publishing, and in particular John Navas for overseeing the production and for making this book possible.

Konstantin Stefanov August 2022

## Author biography

#### Konstantin D Stefanov

Konstantin D Stefanov was born in Rousse, Bulgaria, and has received his MSc in applied physics from Sofia University 'St. Kliment Ohridski'. He received his PhD degree in physics from Saga University, Japan, in 2001. As a research scientist at the Rutherford Appleton Laboratory in Oxfordshire, UK, Dr Stefanov has worked on the development of CCD and CMOS sensors for particle physics. Since 2012 he has been working at the Centre for Electronic Imaging at the Open University, Milton Keynes, UK,

where he is developing CMOS image sensors for scientific and space applications. His research interests are in the areas of physics, technology, and design of CMOS image sensors for science applications, semiconductor device simulations, device characterisation, radiation damage effects, detector electronics and data acquisition systems. He has published over 80 research papers, has co-written two book chapters and holds several patents on CMOS image sensors.

# List of frequently used abbreviations

| AC     | Alternating current                               |

|--------|---------------------------------------------------|

| ADC    | Analogue-to-digital converter                     |

| ADU    | Analogue-to-digital unit                          |

| APS    | Active pixel sensor                               |

| BSI    | Back-side illumination                            |

| CCD    | Charge coupled device                             |

| CDS    | Correlated double sampling                        |

| CG     | Conversion gain                                   |

| CIS    | CMOS image sensor                                 |

| CMOS   | Complementary metal-oxide-semiconductor           |

| CVF    | Charge-to-voltage conversion factor               |

| DC     | Direct current                                    |

| DN     | Digital number                                    |

| DR     | Dynamic range                                     |

| DSNU   | Dark signal non-uniformity                        |

| DUT    | Device under test                                 |

| EO     | Electro-optical                                   |

| ENC    | Equivalent noise charge                           |

| ETF    | Electrical transfer function                      |

| FPN    | Fixed pattern noise                               |

| FSI    | Front-side illumination                           |

| FWC    | Full well capacity                                |

| HDR    | High dynamic range                                |

| IR     | Infrared                                          |

| LED    | Light emitting diode                              |

| MOS    | Metal-oxide-semiconductor                         |

| MOSFET | Metal-oxide-semiconductor field effect transistor |

| MTF    | Modulation transfer function                      |

| MVC    | Mean-variance curve                               |

| NIR    | Near infrared                                     |

| NMOS   | N-channel MOSFET                                  |

| PD     | Photodiode                                        |

| PMOS   | P-channel MOSFET                                  |

| PPD    | Pinned photodiode                                 |

| PRNU   | Photo response non-uniformity                     |

| PTC    | Photon transfer curve                             |

| RMS    | Root mean square                                  |

| RTN    | Random telegraph noise                            |

| RTS    | Random telegraph signal                           |

| SF     | Source follower                                   |

| SNR    | Signal-to-noise ratio                             |

| QE     | Quantum efficiency                                |

| UV     | Ultraviolet                                       |

| 0,     |                                                   |

## Table of common symbols and units

| Symbol              | Description                                  | Value/units                               |

|---------------------|----------------------------------------------|-------------------------------------------|

| α                   | Photon absorption coefficient                | $cm^{-1}$                                 |

| В                   | Signal bandwidth                             | Hz (Hertz)                                |

| $B_n$               | Noise power bandwidth                        | Hz                                        |

| С                   | Capacitance                                  | F (Farad)                                 |

| Cox                 | Area oxide capacitance                       | $F \text{ cm}^{-2}$                       |

| $C_{\rm GS}$        | MOSFET gate-source capacitance               | F                                         |

| $D_n, D_p$          | Diffusion coefficient for electrons or holes | $\mathrm{cm}^2 \mathrm{s}^{-1}$           |

| e <sub>n</sub>      | Voltage noise density                        | $V/\sqrt{Hz}$                             |

| e <sub>nw</sub>     | Voltage white noise density                  | $V/\sqrt{Hz}$                             |

| e <sub>nf</sub>     | Voltage 1/f noise density                    | V (Volts)                                 |

| Ē                   | Electric field                               | $V \text{ cm}^{-1}$                       |

| $E_{\rm a}$         | Activation energy                            | eV                                        |

| $E_{\rm c}$         | Conduction band energy                       | eV                                        |

| $E_{\rm g}$         | Bandgap energy                               | eV                                        |

| $E_{\rm v}$         | Valence band energy                          | eV                                        |

| E <sub>i</sub>      | Intrinsic Fermi level                        | eV                                        |

| $E_{\rm F}$         | Fermi level                                  | eV                                        |

| $E_{t}$             | Trap energy                                  | eV                                        |

| E <sub>e</sub>      | Irradiance                                   | $W \text{ cm}^{-2}$                       |

| $E_{\rm ph}$        | Photon energy                                | eV                                        |

| $E_{\rm w}$         | Ionisation energy                            | eV                                        |

| $\varepsilon_0$     | Dielectric permittivity of vacuum            | $8.85 \times 10^{-14} \text{ F cm}^{-14}$ |

| e <sub>Si</sub>     | Relative dielectric permittivity of silicon  | 11.9                                      |

| f                   | Frequency                                    | Hz                                        |

| $f_{\rm nc}$        | 1/f noise corner frequency                   | Hz                                        |

| $f_{\rm c}$         | Cut-off frequency                            | Hz                                        |

| ν <sub>c</sub><br>Φ | Photon flux                                  | $cm^{-2} s^{-1}$                          |

| •<br>θτ             | Thermal potential, $kT/q$                    | V (Volts)                                 |

| FI<br>G             | Carrier generation rate                      | $cm^{-3} s^{-1}$                          |

| $G_{\rm c}$         | Conversion gain                              | μV/e <sup>-</sup>                         |

| G <sub>SF</sub>     | Source follower gain                         |                                           |

| g <sub>m</sub>      | MOSFET gate transconductance                 | $A V^{-1}$                                |

| sm<br>h             | Planck's constant                            | $6.62 \times 10^{-34} \text{ J s}$        |

| I                   | Current                                      | A (Amperes)                               |

| i <sub>n</sub>      | Current noise density                        | $A/\sqrt{Hz}$                             |

| J                   | Current density                              | $A \text{ cm}^{-2}$                       |

| k                            | Boltzmann constant                                                    | $1.38 \times 10^{-23} \text{ J K}^{-1}$ |

|------------------------------|-----------------------------------------------------------------------|-----------------------------------------|

| Κ                            | System gain                                                           | e <sup>-</sup> /ADU                     |

| $L_n, L_p$                   | Diffusion length for electrons or holes                               | cm                                      |

| λ                            | Photon wavelength                                                     | nm                                      |

| $\mu_n, \mu_p$               | Mobility for electrons or holes                                       | $cm^2V^{-1}s^{-1}$                      |

| n                            | Electron concentration                                                | $\mathrm{cm}^{-3}$                      |

| $n_p$                        | Electron concentration in <i>p</i> -type semiconductor                | $\mathrm{cm}^{-3}$                      |

| $n_{p0}$                     | Electron concentration in <i>p</i> -type semiconductor in equilibrium | $\mathrm{cm}^{-3}$                      |

| NA                           | Acceptor concentration                                                | $\mathrm{cm}^{-3}$                      |

| $N_{\rm D}$                  | Donor concentration                                                   | $\mathrm{cm}^{-3}$                      |

| $N_{ m ss}$                  | Surface trap energy density                                           | $\mathrm{cm}^{-2}\mathrm{eV}^{-1}$      |

| $N_{\rm st}$                 | Surface trap density                                                  | $\mathrm{cm}^{-2}$                      |

| $N_{ m t}$                   | Trap concentration                                                    | $\mathrm{cm}^{-3}$                      |

| р                            | Hole concentration                                                    | $cm^{-3}$                               |

| $p_n$                        | Hole concentration in <i>n</i> -type semiconductor                    | $\mathrm{cm}^{-3}$                      |

| $p_{n0}$                     | Hole concentration in <i>n</i> -type semiconductor in equilibrium     | $\mathrm{cm}^{-3}$                      |

| $P_{\mathrm{ph}}$            | Optical power                                                         | W (Watts)                               |

| Q                            | Charge                                                                | C (Coulomb)                             |

| q                            | Elementary charge                                                     | $1.6 \times 10^{-19} \text{ C}$         |

| R                            | Resistance                                                            | Ω (Ohm)                                 |

| $\sigma, \sigma_n, \sigma_p$ | Trap capture cross section for electrons or holes                     | $\mathrm{cm}^{-2}$                      |

| $S_{ m ph}$                  | Photosensitivity                                                      | $A W^{-1}$                              |

| $S_n$                        | Surface recombination velocity for electrons                          | $\mathrm{cm} \mathrm{s}^{-1}$           |

| t                            | Time                                                                  | s (seconds)                             |

| $	au_n$                      | Electron lifetime                                                     | S                                       |

| Т                            | Temperature                                                           | K, °C                                   |

| U                            | Recombination rate                                                    | $cm^{-3} s^{-1}$                        |

| $U_{ m s}$                   | Surface recombination rate                                            | $cm^{-2} s^{-1}$                        |

| $v_{\rm th}$                 | Electron or hole thermal velocity                                     | $cm s^{-1}$                             |

| v <sub>d</sub>               | Drift velocity                                                        | $\mathrm{cm} \mathrm{s}^{-1}$           |

| $V_{\rm GS}$                 | MOSFET gate-source voltage                                            | V                                       |

| VT                           | MOSFET threshold voltage                                              | V                                       |

**IOP** Publishing

**CMOS** Image Sensors

Konstantin D Stefanov

### Chapter 1

### The fundamentals

#### 1.1 Introduction—what is an image sensor and what does it do?

An image sensor has the job to convert an image, consisting of photons emitted or reflected by an object, into an electronic signal. To register a photon, it must be *absorbed* by the sensor and converted to an electric signal. For most sensors, this happens using the internal photoelectric effect. Once the electric signal is registered and processed, we obtain an electronic image, a representation of the incoming photons. The photon energy can span from the far-infrared up to x-rays.

Image sensors come in a bewildering variety of types, shapes and sizes. Most commonly, image sensors are segmented into individual sensitive elements, called pixels. Each pixel is intended to register photons independently of its neighbours, however, in most real-world sensors there is some electrical and optical crosstalk. An array of pixels forms a 2-D image sensor, which is by far the dominant type, and a line of pixels is a linear array, or 1-D image sensor. A simple photodiode has no pixel structure and can therefore be called a 0-D image sensor.

Typically, we expose the image sensor to photons for a certain time, called integration time. During that time, each pixel absorbs photons and registers an electric signal. The job of the image sensor, broadly speaking, is to determine *how many photons have been received in each pixel during the integration time*. Ideally, every photon should be registered separately, and some image sensors can do exactly that. More often, however, the pure photon-induced signal is mixed with the intrinsic noise of the sensor, and we can find out only the *average* number of registered photons. A linear photoresponse is often desired in an image sensor, so that the electrical output signal is proportional to the number of registered photons. Most sensors have small nonlinearity in their response not exceeding a few percent, but some types have intentionally much stronger nonlinearity, for example with logarithmic response, helping to achieve wide dynamic range.

The output signal from a sensor can be a continuous current proportional to the illumination, and this is the way the photodiodes are normally operated. However,

in low light conditions the photogenerated currents can be extremely small and be counted in few electrons *per second*. Such currents are impossible to measure directly, therefore the method we use is to *integrate* the charge over a certain time on a collection element because this creates a signal that is much easier to measure. Most image sensors, including the ones described in this book, are of the integrating type.

#### **1.2 Charge generation**

#### 1.2.1 Photoeffect

For a semiconductor image sensor to detect light, the photons impinging on it must interact with the sensitive regions of the sensor and be converted to an electric charge, which is then collected and recorded.

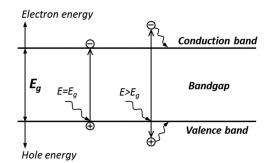

The dominant process of photon conversion in image sensors is the internal photoeffect. An incident photon with sufficient energy can liberate a valence electron from an atom, which becomes a free electron in the conduction band and can move about in the crystal lattice. At the same time, the missing valence electron becomes a hole, which is also mobile, as shown in figure 1.1. In this way, electrons and holes are created in pairs, and the photon is absorbed and disappears. The minimum photon energy for the photoeffect to occur is the bandgap of the semiconductor  $E_g$ . The excess photon energy above this threshold is dissipated as crystal vibrations or by generating secondary electron–hole pairs as the primary pair dissipates its kinetic energy.

Photons with energy lower than the bandgap  $E_g$  are not able to create electronhole pairs, and since there is no other mechanism for photons to lose energy, silicon appears transparent at their wavelength. The photon energy  $E_{ph}$  is given by:

$$E_{\rm ph} = \frac{hc}{\lambda} \tag{1.1}$$

where *h* is Planck's constant, *c* is the velocity of light and  $\lambda$  is the photon's wavelength. Equation (1.1) can be more conveniently written as (1.2) where the photon energy  $E_{\rm ph}$  is in electron-volts (1 eV =  $1.6 \times 10^{-19}$  J) and the wavelength  $\lambda$  is in nanometres:

Figure 1.1. Photoeffect in semiconductors.

$$E_{\rm ph} = \frac{1240}{\lambda} \tag{1.2}$$

Using (1.2) we can calculate that a photon with energy equal to the bandgap of silicon ( $E_{\rm ph} = E_{\rm g} = 1.12$  eV at 300 K) has a wavelength of 1107 nm, and this is commonly referred to as the cut-off wavelength. The bandgap increases slightly at lower temperatures [2] leading to shorter cut-off wavelength and weaker absorption in the near-IR band.

In silicon, as an indirect bandgap semiconductor, the excitation of a valence electron into the conduction band requires that lattice vibrations (phonons) are involved to obey both energy and momentum conservation laws [2]. As the photon energy increases, the amount of momentum transfer must increase too, and the energy required to generate one electron–hole pair gradually increases. Because of this, a photon with energy equal to double the silicon bandgap (2.24 eV, or 554 nm) still generates one electron–hole pair, and not two.

The band structure of silicon has a direct bandgap of 3.1 eV [3] (400 nm) as well, allowing an electron-hole pair to be created directly, without the assistance of a phonon. However, it is thanks to its indirect bandgap that silicon is sensitive to visible light; if it only had the 3.1 eV direct bandgap it would have been sensitive only to wavelengths shorter than 400 nm and unusable for mainstream imaging.

A single electron-hole pair, corresponding to internal quantum yield of unity, is created up to a photon energy equal to three times the bandgap (3.36 eV, or 369 nm) [4]. Above this energy two e-h pairs begin to be created, but at a very low rate. Multiple e-h pair creation becomes significant only when the photon energy exceeds 4 eV (310 nm) [5, 6].

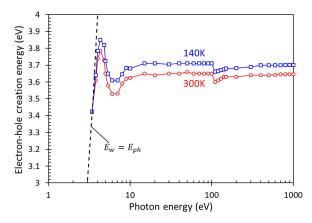

As the photon energy increases further, the ionisation energy  $E_{\rm w}$  needed for the creation of one e–h pair reaches a peak of approximately 4.5 eV [4, 5]. For  $E_{\rm ph} > 10$  eV the pair creation energy  $E_{\rm w}$  levels off to around 3.65 eV, as shown in figure 1.2.

An incoming beam of photons with flux  $\Phi_0$  (number of photons per unit area per second) and energy higher than the bandgap is gradually absorbed in the

Figure 1.2. Electron-hole pair creation energy in silicon at 140 and 300 K (data from [1]). The dashed line marks  $E_{\rm w} = E_{\rm ph}$ .

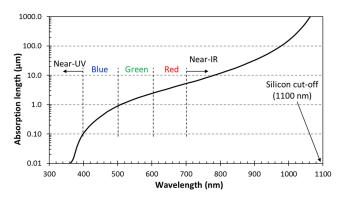

**Figure 1.3.** Photon absorption in silicon for low energy photons from near-UV to near-IR at 300 K. The data is from [7].

semiconductor. Ignoring any reflections, the flux  $\Phi(x)$  at a distance x away from the illuminated surface is given by the Beer–Lambert law:

$$\Phi(x) = \Phi_0 e^{-\alpha x} \tag{1.3}$$

where  $\alpha$  is the absorption coefficient, typically measured in units of cm<sup>-1</sup>. At distance  $x_0 = 1/\alpha$  the incoming photon flux is attenuated by 1/e, which means that 63% of the light has been absorbed. The distance  $x_0$  is called absorption length and is often more practical to use than the absorption coefficient because it allows straightforward comparison with the dimensions used in image sensors.

The absorption length depends strongly on the wavelength of light and changes by a factor of 50 between the lower end (400 nm) and the top end (700 nm) of the visible light range<sup>1</sup>, as shown in figure 1.3 and table 1.1. As the bandgap increases at low temperatures the absorption length increases too, especially at near-IR wavelengths [7]. It is worth noting that photon absorption does not depend on the doping concentration or the free carrier concentration (either electrons or holes) in silicon for most practical cases.

Very often we would like to know what the silicon thickness should be to achieve certain level of photon absorption.

**Example 1.1.** Calculate the silicon thickness for 95% photon absorption for light with 400, 700 and 900 nm wavelength.

**Solution:** 95% absorption means that only 5% of the light is left. From formula (1.3) we have  $e^{-\alpha x} = 0.05$  and therefore  $x = -\ln (0.05)/\alpha = 3.0/\alpha$ . From table 1.1 we get  $1/\alpha = x_0 = 0.105 \,\mu\text{m}$  for 400 nm wavelength, therefore the thickness is  $x = 0.31 \,\mu\text{m}$ . For 700 nm we have  $1/\alpha = 5.263$  and 15.8  $\mu\text{m}$  silicon thickness; and for 900 nm  $x = 97.9 \,\mu\text{m}$ .

<sup>&</sup>lt;sup>1</sup> In the CIE (The International Commission on Illumination) luminous efficiency functions [8] the wavelength range of visibility is 380–700 nm.

**CMOS Image Sensors**

| Wavelength (nm) | Absorption length ( $\mu m$ ) |

|-----------------|-------------------------------|

| 300             | 0.006                         |

| 350             | 0.010                         |

| 400             | 0.105                         |

| 450             | 0.392                         |

| 500             | 0.901                         |

| 550             | 1.565                         |

| 600             | 2.415                         |

| 650             | 3.559                         |

| 700             | 5.263                         |

| 750             | 7.692                         |

| 800             | 11.77                         |

| 850             | 18.69                         |

| 900             | 32.68                         |

| 950             | 63.69                         |

| 1000            | 156.3                         |

| 1050            | 613.5                         |

| 1100            | 2857                          |

**Table 1.1.** Absorption length in silicon for light wavelengths from300 to 1100 nm at 300 K. Data from [7].

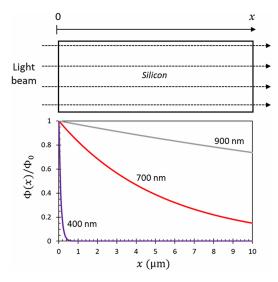

The light attenuation with distance for the wavelengths used in example 1.1 is plotted in figure 1.4 and illustrates the huge differences in silicon thickness required for the same absorption. This example shows the extremes of the visible range; in practice silicon thickness of 5  $\mu$ m is often sufficient for visible light imagers because it allows acceptable absorption in the red end of the spectrum around 600–650 nm.

The fact that in the visible wavelength range each photon creates one electronhole pair can be used to calculate the total light-generated charge in a volume of silicon. This charge, if collected, is the electrical output of the image sensor. Knowing the incident optical power  $P_{\rm ph}$  (measured in watts) and the photon energy we can calculate the number of e-h pairs  $\Delta N_{\rm e-h}$  generated per unit time  $\Delta t$  based on the energy conservation law, simply as this:

$$\frac{\Delta N_{\rm e-h}}{\Delta t} = \frac{P_{\rm ph}}{E_{\rm ph}} \tag{1.4}$$

As we can see the number of generated e-h pairs is inversely proportional to the photon energy, therefore lower energy photons, corresponding to near-IR and red light generate more carriers at the same optical power. While this is true, e-h pair generation requires that the photons are absorbed; for those long wavelengths the silicon must be very thick to ensure full absorption as figure 1.4 tells us.

Figure 1.4. Photon absorption in silicon for violet ( $\lambda = 400$  nm), red ( $\lambda = 700$  nm) and for 900 nm light in the near-infrared.

**Example 1.2.** Calculate the number of e-h pairs generated per second by red light ( $\lambda = 650 \text{ nm}$ ) with an irradiance (power per unit area) of  $E_e = 1 \text{ W m}^{-2}$  in a square pixel with a size a = 10 µm. Assume that the light is fully absorbed in the pixel's volume.

**Solution:** From equation (1.2) we find that for  $\lambda = 650$  nm the photon energy is  $E_{\rm ph} = 1.91$  eV. The energy deposited in the pixel per second is the irradiance multiplied by the pixel area  $a^2$ . The number of generated e-h pairs per second is the energy deposited in the pixel per second, divided by the energy to create one e-h pair:

$$\frac{\Delta N_{\rm e-h}}{\Delta t} = \frac{E_{\rm e}a^2}{qE_{\rm ph}} = \frac{1 \times 10 \times 10^{-6} \times 10 \times 10^{-6}}{1.6 \times 10^{-19} \times 1.91} = 3.27 \times 10^8 \,\rm s^{-1}$$

Here we have multiplied  $E_{\rm ph}$  by the elementary charge q to convert the photon energy from eV to Joules. Irradiance of 1 W m<sup>-2</sup> at 650 nm corresponds to approximately 68.3 lux, or a dimly lit room. This example shows that even meagre illumination manages to create a third of a billion e-h pairs every second in a tiny 10 µm pixel.

If all the e-h pairs were collected, a steady state *photocurrent*  $I_{ph}$  will flow; it is given by multiplying formula (1.4) by the elementary charge to convert the number or e-h pairs per second to coulombs per second, which is current:

$$I_{\rm ph} = \frac{q\Delta N_{\rm e-h}}{\Delta t} \tag{1.5}$$

**Example 1.3.** Calculate the photocurrent flowing in the pixel in example 1.2. Solution: Multiplying the answer by the elementary charge gives:

$$I_{\rm ph} = \frac{q\Delta N_{\rm e-h}}{\Delta t} = 1.6 \times 10^{-19} \times 3.27 \times 10^8 = 5.235 \times 10^{-11} \text{A} = 52.4 \text{ pA}$$

Very often the sensitivity of a semiconductor material is given as the photocurrent per watt of incident light energy. To compare devices irrespective of their structure or pixel size the current can be expressed as *current density*  $J_{ph}$ , i.e. amperes per unit area. If we use the optical power per unit area  $E_e$  (irradiance), equation (1.5) can be rewritten by dividing both sides by the device (or pixel) area, and using (1.4) we get

$$J_{\rm ph} = \frac{qE_{\rm e}}{E_{\rm ph}}.$$

(1.6)

From (1.6) we arrive at the astonishingly simple expression (1.7) for the sensitivity  $S_{\rm ph}$  in terms of detector current density per unit of optical irradiance.  $S_{\rm ph}$  is measured in units of ampere per watt (A W<sup>-1</sup>) because the area cancels from both  $J_{\rm ph}$  and  $E_{\rm e}$ .

$$S_{\rm ph} = \frac{J_{\rm ph}}{E_{\rm e}} = \frac{q}{E_{\rm ph}} \tag{1.7}$$

Equation (1.7) gives the theoretical maximum photosensitivity of an ideal image sensor having perfect light absorption, without any light losses due to reflection, and of course with complete charge collection. The ratio  $E_{\rm ph}/q$  gives the photon energy in units of eV. From here we can calculate that the theoretical maximum photosensitivity for  $\lambda = 650$  nm (as in example 1.2) is  $S_{\rm ph} = 1/1.91 = 0.52$  A W<sup>-1</sup>. Using (1.2), expression (1.7) can also be written as  $S_{\rm ph} = \lambda/1240$ , where  $\lambda$  is in nanometres.

#### 1.2.2 Ionisation

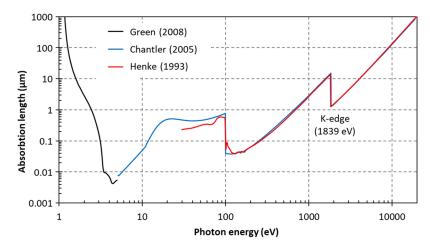

Silicon makes an excellent sensor material not just for the near-IR, visible and UV light, but also for much more energetic photons, such as x-rays. The absorption length covering photon energies from 1.2 eV to 10 keV in figure 1.5 shows what happens at the higher end of silicon's usable range: similarly to the near-IR end, silicon becomes transparent beyond photon energy of about 10 keV. The absorption above 100 eV shows discontinuous absorption edges at the energy levels of the L-shell ( $\approx$ 100 eV) and the K-shell (1839 eV) of the silicon atom. As the photon energy exceeds the binding energy of a shell, the electrons occupying it can be excited and the photon absorption sharply goes up. This corresponds to a stepwise *decrease* in the absorption length, most clearly seen at the K-edge.

For photons with  $E_{\rm ph} > \approx 50$  eV the ionisation energy is  $E_{\rm w} = 3.65$  eV at 300 K [11] and is nearly constant. This allows us to calculate the number of electron-hole pairs  $N_{\rm e-h}$  generated by x-rays and gamma-rays using this simple expression:

$$N_{\rm e-h} = \frac{E_{\rm ph}}{E_{\rm w}} \tag{1.8}$$

Figure 1.5. Photon absorption due to photoeffect in silicon for a wider energy range. Data for <5 eV from [7], 5 - 20000 eV from [9], and >30 eV from [10].

The ionisation energy is temperature dependant; this is due to the reduction of the bandgap as the temperature increases [1, 12]. X-rays in the range 1–10 keV, emitted by radioactive sources and x-ray fluorescence from various materials are particularly useful for sensor characterisation. They are widely used for calibration due to the well-known x-ray energies and the amount of charge created in silicon by them. Also, the initial charge cloud created by low energy x-rays is very compact [13, 14] and this allows the charge to be considered a point source.

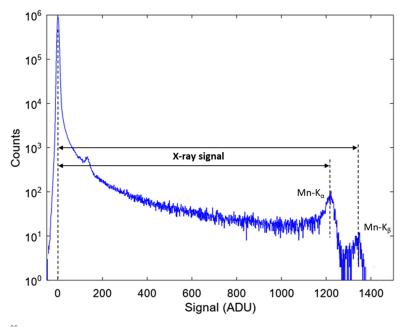

One very popular calibration source is the <sup>55</sup>Fe isotope which decays via electron capture to manganese (<sup>55</sup>Mn) with a half-life of 2.737 years. <sup>55</sup>Mn emits characteristic K-shell x-rays with energies 5.89 keV (Mn-K<sub> $\alpha$ </sub>) and 6.49 keV (Mn-K<sub> $\beta$ </sub>), with probabilities of 24.4% and 2.9%, correspondingly [15]. Figure 1.6 shows an example of a <sup>55</sup>Fe spectrum obtained by a CMOS image sensor.

The absorption length for 5.9 keV photons in silicon is approximately 28  $\mu$ m [10]. This length is much larger than the depth of the active silicon in the typical optical sensor, therefore only a small fraction of the incoming x-rays is absorbed and converted to charge.

**Example 1.4.** Calculate the number of electron-hole pairs generated by the dominant  $Mn-K_{\alpha}$  x-ray, and the current in a pixel receiving one hundred  $Mn-K_{\alpha}$  x-rays per second, assuming that all the charge is collected.

Solution: Using formula (1.8) the number of generated electron-hole pairs per x-ray is

$$N_{\rm e-h} = \frac{E_{\rm K\alpha}}{E_{\rm w}} = \frac{5890}{3.65} = 1614$$

The current for 100 x-rays per second is calculated using (1.5):

$$I_{\rm ph} = \frac{qN_{\rm e-h}}{t} \times 100 = \frac{1.6 \times 10^{-19} \times 1614}{1} \times 100 = 25.8 \,\mathrm{fA}$$

**Figure 1.6.** <sup>55</sup>Fe spectrum obtained by a CMOS image sensor. The peak at 0 ADU is due to pixels without x-ray signal, and the continuum leading to the x-ray peaks is caused by charge collected by more than one pixel.

At much higher photon energies two other mechanisms overtake the photoeffect and begin to play an increasing role—Compton effect and electron–positron pair creation [16]. Besides the detection of optical and x-ray photons, silicon is widely used for the detection of high energy, ionising particles. Traversing the material, charged particles lose energy due to several mechanisms, and most of that energy loss is due to ionisation. The ionisation loss is very high at low particle energies but decreases and flattens off at higher energies in a logarithmic dependence [16]. Particles with energies at and above the plateau, which usually lies at hundreds of MeV, are called minimum ionising particles (MIP).

The average number of the created electron-hole pairs is calculated by the most probable energy loss divided by the ionisation energy as in (1.8). The energy loss due to ionisation has large statistical fluctuations. For particles which lose only a small part of their energy in the material (i.e. the material is 'thin') the energy loss is described by the Landau distribution [17]. In a couple of microns of silicon there is a significant probability that a traversing high energy particle will cause no ionisation at all [18]. At the same time, the probability that the energy loss can far exceed the most probable value is also significant, due to the long tail in the Landau distribution.

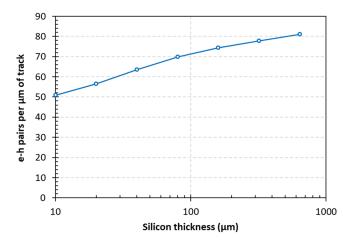

The most probable number of e-h pairs increases with the thickness, as shown in figure 1.7, and above 10  $\mu$ m the energy loss begins to approach the Landau distribution.

#### **1.3 Charge collection**

In the previous section we looked at how photons generate free charge, consisting of electrons and holes, and how the amount of charge depends on the photon energy. The question now is how to collect this charge and measure it.

Figure 1.7. Most probable number of electron-hole pairs per micrometre of track for high energy charged particles, data from [17].

Left on its own, the charge will simply diffuse out, never to be seen again. Diffusion is fundamental in nature and always occurs when there is a difference in carrier concentration. The charge generated in pixels receiving more illumination will diffuse towards pixels receiving less illumination, until we get nearly uniform charge 'blob' everywhere. Obviously, this is not what we want to happen in an image sensor.

We need a charge collecting element—something that is electrically attractive to either electrons or holes (but obviously cannot be attractive to both). To make the charge move in a particular direction for collection we need to create an *electric field*; within it the charge experiences an electrostatic force and begins to accelerate in a direction opposite to the field (for electrons) and along the field (for holes). This charge movement in the presence of electric field is called *drift* and is the primary mechanism for charge collection. During drift the charge continues to diffuse due to its concentration gradient, regardless of the presence of any electric field; this is unavoidable but not always undesirable.

#### 1.3.1 Carrier lifetime

An important point in image sensor operation, which often goes without much mention, is that the generated e-h pairs must survive, i.e. not recombine or get trapped, for sufficiently long time so that they can be collected. The characteristic describing the 'life duration' of electrons and holes is called *carrier lifetime* [19] and is widely used in semiconductor physics. What 'sufficiently long' means in practice will be explored in the next two sections. As a rough indicator the charge collection time rarely exceeds a few hundreds of nanoseconds, and this is how long the carriers must survive. Carrier lifetime can be many orders of magnitude longer, especially in high quality epitaxial silicon.

Whenever electrons and holes are created, for example by illumination with light, the excess carrier concentration will decay back to equilibrium after the source of e-h pair generation is turned off. In silicon the dominant physical mechanism for the decay is trap-assisted recombination. Direct e-h recombination occurs too, but at a much smaller rate. The rate of decay towards the equilibrium concentration, expressed as the change of carrier concentration per unit time  $U = \Delta n / \Delta t$ , is called *recombination rate*. The simplest possible mathematical description of this process is to assume that the recombination rate U is proportional to the excess carrier concentration. For example, if the electron concentration in *p*-type silicon is  $n_p$  and the equilibrium concentration is  $n_{p0}$ , the recombination rate can be written as  $U \propto (n_p - n_{p0})$ . Since proportionality is assumed, we need a proportionality constant in units of seconds, so that the recombination rate is measured in units of carrier concentration  $\tau_p$  for holes) and can be thought of as the characteristic time over which the carrier concentration decreases. Now, the recombination rate can be written in its familiar form:

$$U = -\frac{dn_p}{dt} = \frac{n_p - n_{p0}}{\tau_n}$$

(1.9)

We have added a negative sign in (1.9) because due to recombination the carrier concentration decreases  $(dn_p/dt < 0)$  when  $n_p - n_{p0} > 0$ , and U > 0. Because  $n_{p0}$  is constant, we can write that

$$\frac{d(n_p - n_{p0})}{dt} = -\frac{n_p - n_{p0}}{\tau_n}$$

(1.10)

and after separating the variables we can integrate both sides:

$$\int \frac{d(n_p - n_{p0})}{n_p - n_{p0}} = -\frac{1}{\tau_n} \int dt$$

(1.11)

$$\ln(n_p - n_{p0}) + \text{const} = -\frac{t}{\tau_n}$$

(1.12)

The final equation can be written by using the initial conditions: at t = 0 the excess electron concentration is  $n_p(0) - n_{p0}$  and at  $t \to \infty$  naturally  $n_p - n_{p0} = 0$ , with only the equilibrium concentration  $n_{p0}$  left. Therefore, the constant in equation (1.12) must equal  $-\ln(n_p(0) - n_{p0})$  and we arrive at the time dependence of  $n_p$ :

$$n_p(t) = n_{p0} + (n_p(0) - n_{p0})e^{-\frac{t}{\tau_n}}$$

(1.13)

Equation (1.13) tells us that the electron lifetime  $\tau_n$  is the characteristic time over which the excess carrier concentration decreases by 1/e, i.e. only 37% of the excess carriers remain. After three times the lifetime only 5% of the initial charge will be left.

#### 1.3.2 Recombination

This is a good place to answer an important question: why don't the electrons and the holes recombine immediately after they are generated? After all, they are created together and close to each other, and it would be reasonable to expect that they should recombine at high rate. Fortunately, such direct (band-to-band) recombination in silicon is very rare because it is an indirect bandgap semiconductor. Carrier lifetime controlled by band-to-band recombination is very long; in high purity silicon the electron and hole lifetimes can be many milliseconds. This long lifetime allows the charge to diffuse out a long distance from the place it was generated without recombining, unless it is quickly collected with the help of an electric field.

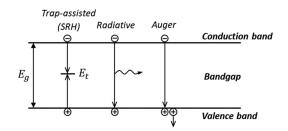

Figure 1.8 shows two direct, and very rare band-to-band recombination mechanisms: radiative with the emission of a photon, and Auger recombination where the excess energy is transferred to another carrier, such as a hole in highly doped *p*-type silicon.

The third one, trap-assisted recombination via a mid-band trap, is by far the dominant mechanism in silicon, described by the Shockley–Read–Hall (SRH) theory [20]. Traps are produced by imperfections or impurities in the crystal lattice, which introduce energy levels deep in the bandgap. Traps take part in both capture and emission of carriers and are also called generation-recombination centres.

The recombination rate from a trap with concentration  $N_t$  and energy level  $E_t$  above the valence band is given by

$$U = \frac{\sigma_n \sigma_p v_{\rm th}(pn - n_i^2) N_l}{\sigma_n \left[ n + n_i \exp\left(\frac{E_l - E_i}{kT}\right) \right] + \sigma_p \left[ p + n_i \exp\left(-\frac{E_l - E_i}{kT}\right) \right]}$$

(1.14)

Here  $E_i$  is the intrinsic Fermi level (approximately the mid-band energy level); k is the Boltzmann's constant;

T is the absolute temperature;

$v_{\rm th}$  is the carrier thermal velocity;

$n_i$  is the intrinsic carrier concentration;

n and p are the electron and hole concentrations, respectively;

$\sigma_n$  and  $\sigma_p$  are the electron and hole capture cross-sections, respectively.

Figure 1.8. Recombination mechanisms.

The maximum recombination rate occurs when the denominator is at its minimum, achieved when  $E_t = E_i$ . This indicates that mid-band traps are the most effective in limiting the carrier lifetime.

In a *p*-type semiconductor we have  $p \gg n_i$  and  $p \gg n$ , and if the two capture cross-sections are similar ( $\sigma_n \cong \sigma_p$ ), the second term in the denominator of (1.14) becomes much larger than the first. Therefore, we can write that

$$U \approx \frac{\sigma_n v_{\rm th} (pn - n_i^2) N_t}{p}$$

(1.15)

Introducing a small excess concentration of electron-hole pairs does not change significantly the equilibrium hole concentration  $p_{p0}$  in *p*-type silicon. Using that  $p \approx p_{p0}$  and  $n_i^2 = p_{p0}n_{n0}$  [21], equation (1.15) can be written as

$$U \approx \frac{\sigma_n v_{th} (p_{p0} n_p - p_{p0} n_{n0}) N_t}{p_{p0}} = \sigma_n v_{th} N_t (n_p - n_{n0})$$

(1.16)

Comparing with (1.9) we see that the term multiplying the concentration difference is the inverse of the electron lifetime (also called recombination lifetime)

$$\tau_n = \frac{1}{\sigma_n v_{\rm th} N_t} \tag{1.17}$$

Typical capture cross-sections are in the range  $10^{-16}$  to  $10^{-14}$  cm<sup>2</sup>.

**Example 1.5.** Calculate the electron lifetime due to a mid-band trap  $(E_t = E_i)$  with  $\sigma_n = 10^{-15}$  cm<sup>2</sup> and concentration  $10^{12}$  cm<sup>-3</sup>, using that the electron thermal velocity is  $v_{\text{th}} = 1.4 \times 10^7$  cm s<sup>-1</sup>.

Solution: Using (1.17) we get

$$\tau_n = \frac{1}{10^{-15} \times 1.4 \times 10^7 \times 10^{12}} = 71.4 \,\mu\text{s}$$

To put this into perspective, trap concentration of  $10^{12}$  cm<sup>-3</sup> corresponds to an average of one trap per cubic micrometre, or one trap per 50 billion Si atoms.

Measurements show that in high quality, lightly doped ( $<10^{15}$  cm<sup>-3</sup>) silicon the minority carrier lifetime can be tens of milliseconds [22]. Considering the calculation in example 1.5, this implies that the trap density responsible in the SRH model must be less than  $10^{10}$  cm<sup>-3</sup>, or one trap per 5 trillion atoms. As the dopant concentration increases above  $10^{16}$  cm<sup>-3</sup> the lifetime begins to decrease and this is taken into account as concentration-dependent SRH lifetime [23].

At high carrier density, such as along a dense ionisation track or in solar cells, Auger and band-to-band radiative recombination can begin to limit the lifetime even in low-doped silicon. Auger recombination involves a direct recombination between an electron and a hole, with the excess energy transferred to another electron or hole. The Auger lifetime for high excess carrier concentration in a lightly doped semiconductor is [22]:

$$\tau_{\text{Auger}} = \frac{1}{C_a \Delta n^2} \tag{1.18}$$

Here  $C_a$  is the ambipolar Auger coefficient (1.66 × 10<sup>-30</sup> cm<sup>6</sup> s<sup>-1</sup> in silicon [24]) and  $\Delta n = n_p - n_{n0}$  or  $\Delta n = p_n - p_{p0}$  is the excess carrier concentration.

The lifetime due to band-to-band radiative recombination is given by

$$\tau_{\rm rad} = \frac{1}{B\Delta n} \tag{1.19}$$

where  $B = 4.7 \times 10^{-15}$  cm<sup>3</sup> s<sup>-1</sup> is the radiative coefficient in silicon at 300 K [25]. It is easy to see that the Auger and radiative lifetimes are much larger than  $\tau_{\text{SRH}}$  and can become comparable to the SRH lifetime only at excess concentration above  $10^{16}-10^{17}$  cm<sup>-3</sup>. In a typical image sensor, the excess carrier concentration due to illumination rarely exceeds  $10^8-10^{10}$  cm<sup>-3</sup>, therefore the direct recombination mechanisms have negligible influence.

The total lifetime  $\tau_{tot}$  can be calculated from Matthiessen's rule for the three recombination processes as in [19]

$$\frac{1}{\tau_{\rm tot}} = \frac{1}{\tau_{\rm SRH}} + \frac{1}{\tau_{\rm Auger}} + \frac{1}{\tau_{\rm rad}}$$

(1.20)

Equation (1.20) is analogous to the one used to calculate the resistance of parallel resistors; physically it means that the different recombination mechanisms work independently and in parallel.

#### 1.3.3 Drift

We are going to consider a hypothetical collection element without specifying what it is and how it is made; then in the following section we will talk about two real charge collection elements—the *pn* junction and the MOS capacitor.

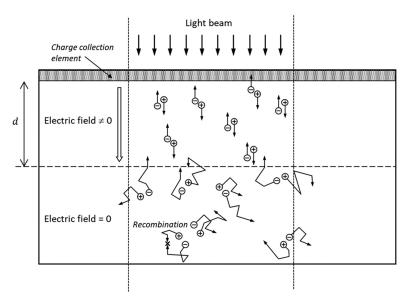

Figure 1.9 shows our hypothetical collection element. From the surface down to depth d there is a constant electric field E, and below d the field is zero. This may look artificial but is not far off from reality.

In this structure only the electrons are collected, and the holes are discarded never to be seen again, as is typical for most image sensors. Electrons are preferred because they move much faster than the holes, resulting in shorter collection times. Holes are allowed to diffuse until they reach the backside substrate electrode, or they recombine after travelling a long distance away from the charge collection element.

Within a region having an electric field E electrons experience a force F = -qEand begin to accelerate. Holes experience the same force but with the opposite sign and move in the other direction. As mentioned previosly, this movement under the influence of an electric field is called *drift*. In semiconductors it is experimentally

Figure 1.9. Charge collection of electrons created by a light beam and experiencing drift and diffusion.

observed that at low electric fields ( $< \sim 10^4 \text{ Vcm}^{-1}$ ) the charge carriers acquire drift velocity  $v_d$  proportional to the electric field *E*:

$$v_{\rm d} = \mu E \tag{1.21}$$

The proportionality factor  $\mu$  is called *mobility* and is not a constant—it decreases as the temperature and the doping concentration increase [26]. The electron mobility  $\mu_n$  at low fields is about three times higher than the hole mobility  $\mu_p$ ; the values in low-doped silicon at 300 K are  $\mu_n = 1400 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and  $\mu_p = 470 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  [26]. The higher electron mobility and velocity is one of the main reasons why we prefer collecting and transferring electrons, rather than holes.

The drift velocity decreases below the value calculated by (1.21) at higher electric fields (above 10<sup>4</sup> V cm<sup>-1</sup>), and stops increasing altogether (i.e. saturates) at  $E > 10^5$  V cm<sup>-1</sup>. The saturation drift velocity  $v_d^{sat}$  for both electrons and holes is approximately 10<sup>7</sup> cm s<sup>-1</sup>.

Drift velocity is directional and determined by the applied electric field; it is also superimposed on the thermal carrier velocity caused by their random movement in the crystal lattice. The thermal velocity for electrons is given by

$$v_{\rm th} = \sqrt{\frac{3kT}{m_0^*}} \tag{1.22}$$

where k is the Boltzmann constant, T is the absolute temperature and  $m_0^* = 0.26m_0$ is the effective electron mass [2]. At 300 K formula (1.22) gives  $v_{\text{th}} = 2.3 \times 10^7$  cm s<sup>-1</sup>. This is similar to the experimentally observed saturation velocity  $v_d^{\text{sat}}$ , and is an indication that the simple proportionality in formula (1.21) is valid only when  $v_d \ll v_{\text{th}}$ . **Example 1.6.** Calculate the electron drift velocity for  $E = 1000 \text{ V cm}^{-1}$  and electron mobility  $\mu_n = 1400 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  (value for Si at 300 K and for low doping concentration), and compare it to the thermal velocity  $v_{\text{th}}$ . **Solution:** From formula (1.21) we get

$$v_{\rm d} = \mu_n E = 1400 \times 1000 = 1.4 \times 10^6 \, {\rm s}^{-1}$$

This velocity is about 20 times lower than the random thermal electron velocity.

Knowing the drift velocity allows us to calculate the time it takes to collect the charge. For simplicity we can consider that  $v_d$  is much smaller than the saturation velocity. The travel distance x is simply the velocity multiplied by the time:

$$x = v_{\rm d}t = \mu_n Et \tag{1.23}$$

The charge collection time t is the device thickness divided by the drift velocity, and substituting the drift velocity from (1.21) we arrive at:

$$t = \frac{d}{v_{\rm d}} \cong \frac{d}{\mu_n E} = \frac{d^2}{\mu_n V} \tag{1.24}$$

Here we have used that the electric field is the applied voltage V divided by the thickness d. This is an approximate and simple, but very useful formula; we will refine it further in the following sections.

**Example 1.7.** Calculate the charge collection time in silicon with thickness  $d = 5 \,\mu\text{m}$  and applied voltage across it V = 1 V. The electron mobility is  $\mu_n = 1400 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . Compare with the charge collection time under velocity saturation ( $v_d^{\text{sat}} \cong 10^7 \text{ s}^{-1}$ ). Solution: First, we need to see how the electron drift velocity compares to the saturation velocity. Using (1.21)

$$v_{\rm d} = \mu_n E = \mu_n \frac{V}{d} = 1400 \times \frac{1}{5 \times 10^{-4}} = 2.8 \times 10^6 \,\mathrm{s}^{-1}$$

we see that it is about a factor of 3 lower than  $v_d^{\text{sat}}$ , therefore formula (1.24) can be used and gives:

$$t = \frac{(5 \times 10^{-4})^2}{1400 \times 1} = 0.18 \text{ ns}$$

The collection time under velocity saturation is calculated as

$$t = \frac{d}{v_{\rm d}^{\rm sat}} = \frac{5 \times 10^{-4}}{10^7} = 0.05 \,\rm ns$$

This example shows that for the typical sensor thicknesses the charge collection time by drift is very short and may become an issue only if very fast operation is required. However, in a much thicker sensor, made so that it can have higher absorption at near-IR wavelengths, the charge collection time could be substantially longer due to the quadratic dependence on the device thickness.

#### 1.3.4 Diffusion

Charge generated in a field-free semiconductor diffuses out from the point at which it is created and can travel large distances. It can reach a region with an electric field, where it is swept away, or it can recombine with the assistance of bulk or surface traps.

If we generate a point-like sphere of electron-hole pairs, they will expand stochastically in a cloud described by the Gaussian distribution. After time t, the RMS cloud radius  $r_n$  for electrons and  $r_p$  for holes in one dimension is given by:

$$r_n = \sqrt{2D_n t} \tag{1.25}$$

$$r_p = \sqrt{2D_p t} \tag{1.26}$$

where  $D_n$  is the diffusion coefficient for electrons and  $D_p$  for holes, measured in cm<sup>2</sup> s<sup>-1</sup>. The diffusion coefficients are connected to the mobility via the Einstein relationship:

$$D_n = \mu_n \frac{kT}{q} \tag{1.27}$$

$$D_p = \mu_p \frac{kT}{q} \tag{1.28}$$

The diffusion radii are the standard deviations of the charge density spread; from the properties of the Gaussian distribution, we know that 95% of the charge is contained within radius  $2r_n$  for electrons and  $2r_p$  for holes.

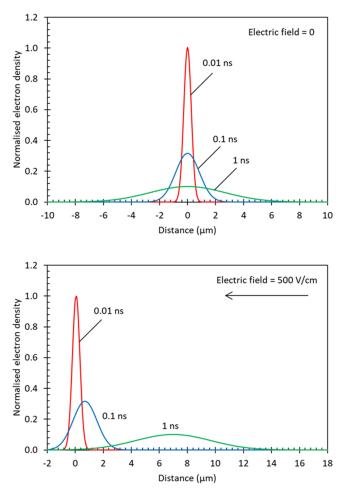

Figure 1.10 shows the diffusion spread with time of a point-like charge generated at t = 0 without any recombination. The electron density is described by a Gaussian with standard deviation given by (1.25), with the peak moving by a distance x determined by (1.23) when the electric field is not zero.

Electrons spread  $\sqrt{3}$  times faster than holes due to their diffusion coefficient being three times higher; the values can be calculated from (1.29) and (1.30) and are  $D_{\rm n} = 36 \text{ cm}^2 \text{ s}^{-1}$ ,  $D_{\rm p} = 12 \text{ cm}^2 \text{ s}^{-1}$  at 300 K.

During diffusion the charge carrier concentration decreases because they spread out; at the same time their concentration decreases also because they are subjected to various recombination processes, with their combined influence reflected in the carrier lifetime. The longest distance the carriers can travel is naturally limited by their lifetime and is called *diffusion length*. It is an important parameter in semiconductors and enters numerous formulas describing image sensor operation. The diffusion length  $L_n$  for electrons is defined by:

Figure 1.10. Electron spread only due to diffusion (at zero electric field) and due to drift and diffusion with electric field =  $500 \text{ V cm}^{-1}$  (after [2], p 55).

$$L_n = \sqrt{D_n \tau_n} \tag{1.29}$$

μm

and a similar expression can be written for hole diffusion length  $L_p$ . The diffusion length is usually much larger than the typical pixel sizes due to the long carrier lifetime.

**Example 1.8.** Calculate the diffusion length for electrons in silicon with electron lifetime  $\tau_n = 1$  ms (fairly typical for low-doped, high quality epitaxial silicon). The diffusion coefficient is  $D_n = 36$  cm<sup>2</sup> s<sup>-1</sup>. **Solution:**

$$L_n = \sqrt{36 \times 10^{-3}} = 1897$$

This is a *really long* distance; some image sensors are physically smaller than this!

Since charge travels so well on its own, can we collect it using only diffusion? The short answer is 'No'—collection entirely by diffusion can lead to significant losses because the charge is not going to stay in the confines of the pixel where it was generated. Diffusion is isotropic, and charge moves in all directions. To capture it, we need the collection element to surround the charge on all sides, or a special structure that forces the charge to go in one predominant direction.

Drift is a far better choice for charge collection because it is directional towards the source of electric field. It is also much faster and minimises the chance of charge loss. The distance travelled under drift (1.23) is proportional to time, while the diffusion radius (1.25) increases much slower as a square root. Also, electrons move three times faster than holes in electric field and not only  $\sqrt{3}$  times faster as in diffusion.

**Example 1.9.** Calculate the electron collection time if the charge moves only by diffusion for the values in example 1.7, assuming that the charge is forced to travel in one direction, and there is no charge loss.

**Solution:** Using equation (1.25) we can calculate the time it takes the electrons to travel the longest distance, equal to the depth of the sensor  $r_n = d = 5 \ \mu m$ :

$$t = \frac{r_n^2}{2D_n} = \frac{(5 \times 10^{-4})^2}{2 \times 36} = 3.5 \text{ ns}$$

Because of the stochastic nature of the diffusion this time can be considered as a time constant; three time constants would suffice for 95% charge collection, and equals to 10.5 ns. This time is two orders of magnitude longer than in charge collection by drift.

#### **1.4 Charge transfer**

After the charge is collected it needs to be converted to a voltage or a current that can be measured using electronic circuits. This could happen at the collection element itself, but very often the tasks of collection and conversion are physically separated for good reasons. The charge needs to travel to a dedicated place where it is converted to an electrical signal; therefore, the task is to perform an efficient *charge transfer*.

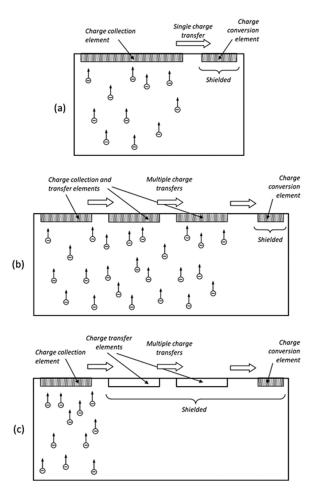

Figure 1.11 shows schematically three cases of charge transfer. Figure 1.11(a) corresponds to CMOS image sensors using pinned photodiode as a collection element and is probably the most widely used. Here the photogenerated electrons are directed to the collection element by an electric field. The conversion element is shielded from direct charge collection and receives only the charge transferred to it. This is usually accomplished by either an optical shield over the conversion element, or electrically—by steering the electrons away from it.

**Figure 1.11.** Charge transfer in image sensors: (a) single transfer; (b) multiple transfers with charge collection elements capable of charge transfer; (c) multiple transfer with dedicated transfer elements which do not collect charge.

Figures 1.11(b) and 1.11(c) show examples where the charge travels larger distances, and the transfer is done is many steps. The transfer elements can either be the same as the charge collection elements, as in full frame CCDs, or they can be dedicated to charge transport only, as in interline transfer CCDs.

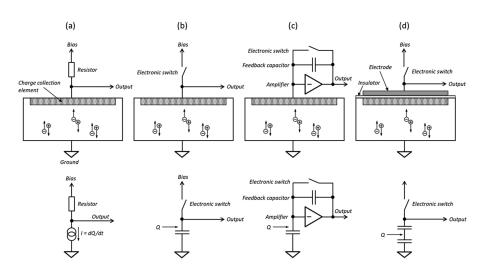

## 1.5 Charge conversion

Charge conversion is a crucial step that occurs at a *sense node*, where the charge is converted to an electrical signal—most frequently a voltage. This can happen *destructively*—meaning that after the conversion the charge cannot be recovered or returned to its original state. This is the typical conversion in image sensors.

The conversion can also occur *non-destructively*, which is when the charge remains unaltered and intact, and the same charge can be converted multiple times.

A circuit allowing non-destructive conversion would normally couple capacitively to the charge without getting in physical contact with it.

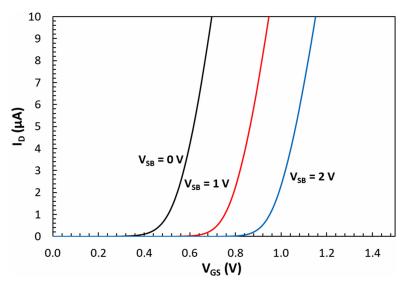

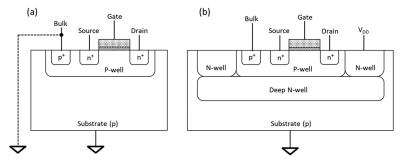

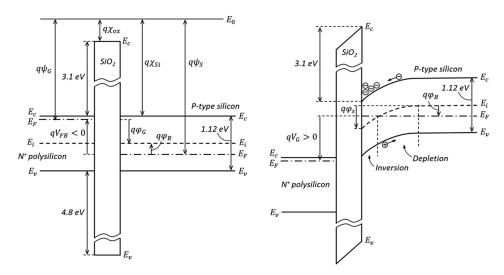

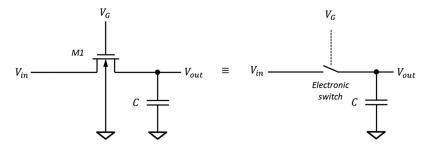

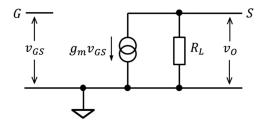

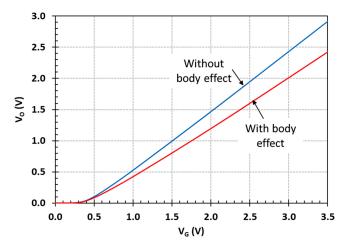

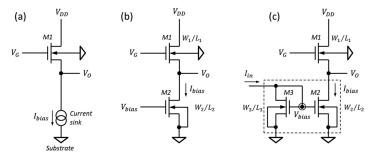

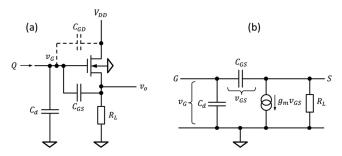

Why is destructive conversion preferred? Because it is more sensitive and a larger electrical signal can be obtained for the same charge, it is usually sufficient to convert the signal into voltage only once. Multiple signal measurements requiring nondestructive conversions are used only in some specialised sensors where they offer some advantages, such as charge measurement during collection, or for noise reduction.