## **LETTER • OPEN ACCESS**

## Thin channel $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs with self-aligned refractory metal gates

To cite this article: Kyle J. Liddy et al 2019 Appl. Phys. Express 12 126501

View the article online for updates and enhancements.

## You may also like

- Design of selective-area growth compatible fully-vertical GaN p-i-n diodes with dielectric vertical sidewall appended edge termination schemes

Palash Sarker, Frank P Kelly, Matthew Landi et al.

- A state-of-art review on gallium oxide fieldeffect transistors

Rundi Qiao, Hongpeng Zhang, Shuting Zhao et al.

- Automatic Detection of Sunspots on Fulldisk Solar Images Using the Simulated Annealing Genetic Method Yunfei Yang, Hongjuan Yang, Xianyong Bai et al.

https://doi.org/10.7567/1882-0786/ab4d1c

## Thin channel β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs with self-aligned refractory metal gates

Kyle J. Liddy<sup>1\*</sup>, Andrew J. Green<sup>2</sup>, Nolan S. Hendricks<sup>2</sup>, Eric R. Heller<sup>3</sup>, Neil A. Moser<sup>2</sup>, Kevin D. Leedy<sup>2</sup>, Andreas Popp<sup>4</sup>, Miles T. Lindquist<sup>1</sup>, Stephen E. Tetlak<sup>2</sup>, Günter Wagner<sup>4</sup>, Kelson D. Chabak<sup>2</sup>, and Gregg H. Jessen<sup>2</sup>

<sup>1</sup>KBR, Inc., Air Force Research Laboratory Sensors Directorate, WPAFB, OH 45433, United States of America

Received September 9, 2019; revised September 23, 2019; accepted October 10, 2019; published online October 29, 2019

We report the first demonstration of self-aligned gate (SAG)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistors (MOSFETs) as a path toward eliminating source access resistance for low-loss power applications. The SAG process is implemented with a subtractively defined and etched refractory metal, such as Tungsten, combined with ion-implantation. We report experimental and modeled DC performance of a representative SAG device that achieved a maximum transconductance of 35 mS mm<sup>-1</sup> and an on-resistance of ~30  $\Omega$  mm with a 2.5  $\mu$ m gate length. These results highlight the advantage of implant technology for SAG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs enabling future power switching and RF devices with low parasitic resistance. Not subject to copyright in the USA. Contribution of Wright-Patterson AFB

nterest in beta-phase Gallium Oxide (β-Ga<sub>2</sub>O<sub>3</sub>) as a nextgeneration ultra-wide bandgap semiconductor is due to its potential for use in high efficiency power applications.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> possesses a bandgap of  $\sim$ 4.8 eV with an estimated critical field strength ( $E_c$ ) of  $\sim 8 \, \mathrm{MV \, cm}^{-1}$  which is  $2 - 3 \times$ higher than GaN and SiC. 1,2) Power switching conduction losses, defined by Baliga's figure of Merit,3) are a cubic function of  $E_c$ , and empirical  $E_c$  values for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> have already surpassed the theoretical limits for GaN and SiC.<sup>4)</sup> β-Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistors (MOSFETs) have demonstrated the ability to block high voltages near and surpassing 1 kV in depletion<sup>5–9)</sup> and enhancement  $^{10,11)}$  mode operation. For  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> RF devices, the Johnson's figure of Merit<sup>12)</sup> compares favorably to GaN as reports of modeled saturation velocity reach as high as  $\sim 2 \times 10^7 \, \text{cm s}^{-1.13}$  Low-GHz  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> RF power devices have been reported<sup>14)</sup> as well as high frequency small signal results with T-gates. 15,16)

Most early device results, however, suffer heavily from resistive parasitic losses both in the drift ( $R_{\text{drift}}$ ) and source access ( $R_S$ ) regions. The  $R_S$  is a critical device parameter that limits device transconductance ( $G_M$ ) expressed as:

$$G_{M,\text{ext}} \approx G_{M,\text{int}} \cdot (1 + R_s \cdot G_{M,\text{int}})^{-1}.$$

(1)

$G_{M,\rm ext}$  is the extrinsic  $G_M$  measured in saturation with parasitic losses and  $G_{M,\rm int}$  is the intrinsic value. Removal of parasitic resistance such as access resistance ( $R_{S,\rm access}$ ) is imperative for lateral device scaling due to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>'s low mobility relative to other materials. For example, the sheet resistance of GaN HEMTs are typically at least an order of magnitude lower than previously reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channels.

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> is amenable to Si ion-implant; therefore, it is the only semiconductor material with a band gap larger than SiC that can be designed with a self-aligned gate (SAG) process. A SAG process was previously reported for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> that eliminated  $R_{S,access}$  with better DC performance compared to non-SAG devices. <sup>17)</sup> Here, we expand on the SAG process, device characterization and benchmark the results. The measured  $G_{M,ext}$  and  $I_{DS}$  is among the highest measured for Ga<sub>2</sub>O<sub>3</sub> MOSFETs. A Sentaurus TCAD device simulation is

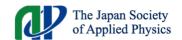

Fig. 1. (Color online) (a) Schematic of a SAG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET, (b) top-down SEM image of a representative 2 × 50 SAG MOSFET with a dashed line indicating the cross-sectioned region, (c) TEM image of gated region showing gate metals and Al<sub>2</sub>O<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interface, (d) HR-TEM image of the W gate electrode, gate oxide and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate, and (e) HR-TEM of the gate oxide and implanted  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel.

included to support the measured data and predict performance with deep sub-micron gate length scaling.

The device sample was prepared with a single 22 nm thick Si-doped  $\beta\text{-}Ga_2O_3$  homoepitaxial channel layer grown by metal organic vapor phase epitaxy directly on a semi-insulating (010) Fe-doped substrate at Leibniz-Institut für Kristallzüchtung -Berlin, Germany. The device fabrication process began by depositing  $\sim\!30\,\mathrm{nm}$  of  $Al_2O_3$  by plasma-enhanced atomic layer deposition to serve as the gate dielectric as well as an implant cap. Next, a W refractory metal layer was sputtered and patterned with a Cr hard mask to subtractively define a 2.5  $\mu\mathrm{m}$  W/Cr gate electrode with SF\_6 reactive ion etch (RIE) chemistry. A refractory metal gate is

Content from this work may be used under the terms of the Creative Commons Attribution 4.0 license. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

<sup>&</sup>lt;sup>2</sup>Air Force Research Laboratory Sensors Directorate, WPAFB, OH 45433, United States of America

<sup>&</sup>lt;sup>3</sup>Air Force Research Laboratory Materials and Manufacturing Directorate, WPAFB, OH 45433, United States of America

<sup>&</sup>lt;sup>4</sup>Leibniz-Institut für Kristallzüchtung (IKZ), Berlin, Germany

<sup>\*</sup>E-mail: kyle.liddy.ctr@us.af.mil

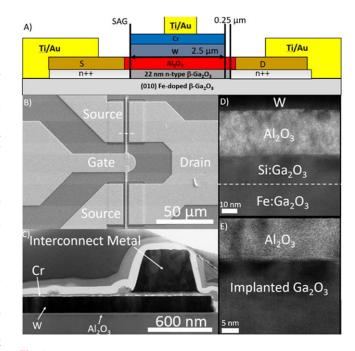

Fig. 2. (Color online) Linear transfer (a), log transfer (b) and output (c) characteristics of an experimental and modeled SAG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET with  $L_G = 2.5 \mu m$  and  $L_{SD} = 2.75 \mu m$ , as well as the projected electrical performance of a SAG MOSFET with  $L_G = 0.5 \mu m$  and  $L_{SD} = 0.75 \mu m$  to show expected effect of device scaling.

vital to a self-aligned process because an Au-based gate metal stack would not remain intact at the required implant activation temperature. Si-implant regions were then patterned with the source-side of the W/Cr gate exposed to eliminate the gate-source region ( $L_{GS} = 0 \mu m$ ), while the gate-drain distance ( $L_{\rm GD}$ ) remained, measuring 0.25  $\mu$ m. A shallow Si-implant profile was designed with 10 and 35 keV energies with a total dose of  $1 \times 10^{15}$  ions cm<sup>-2</sup> to achieve a target  $1 \times 10^{20} \, \text{cm}^{-3}$  doping concentration. The Si-implant was activated at 900 °C for 120 s using rapid thermal annealing (RTA) in a N2 ambient. Ohmic contact to the implanted regions was achieved with a Ti/Al/Ni/Au evaporated metal stack followed by a 470 °C RTA process for 1 min in a N<sub>2</sub> ambient after removing the implant cap with RIE. Electrical isolation was achieved with inductively coupled plasma/reactive ion etching. Finally, additional Ti/Au gate and interconnect metal was added for device characterization.

Displayed in Fig. 1(a) is a schematic of a representative  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SAG MOSFET. The source–drain distance ( $L_{\rm SD}$ ) between the implanted regions is  $\sim$ 2.75  $\mu$ m and the gate length ( $L_G$ ) is  $\sim$ 2.5  $\mu$ m. Van der Pauw test structures were measured after fabrication to track sheet charge density ( $n_{\rm sh}$ ), sheet resistance ( $R_{\rm sh}$ ) and mobility ( $\mu$ ) with average

values of  $n_{\rm sh}=4.96\times10^{12}\,{\rm cm}^{-2},~R_{\rm sh}=2.6\times10^4\,\Omega\,{\rm sq}^{-1},$  and  $\mu=48.4\,{\rm cm}^2\,{\rm V}^{-1}\,{\rm s}^{-1},$  respectively. The  $R_{\rm sh}$  and  $R_C$  of the implanted regions are on the order of  $2.0\times10^3\,\Omega\,{\rm sq}^{-1}$  and  $1.5\,\Omega$  mm respectively based on measurements from samples with a similar doping profile.

A scanning electron microscope image of the  $2\times50$  SAG MOSFET is shown in Fig. 1(b). High-resolution transmission electron microscopy (HR-TEM) inspection images of the SAG MOSFET were prepared in the regions under the gate and on the source-side of the gate with Si ion-implantation [see Figs. 1(c)–1(e)]. Lattice planes of (010)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> are visible in the implanted region showing no structural defect following the implant activation anneal. Similarly, the gate dielectric appears preserved after 900 °C implant activation with no indication of polycrystalline domains, and the W gate electrode maintains a sharp interface with the gate dielectric layer.

The DC I–V characteristics of the SAG MOSFET are shown in Figs. 2(a)–2(c). The transfer curve is shown in Fig. 2(a) indicating a maximum  $G_M = 35 \text{ mS mm}^{-1}$  measured at  $V_{\rm DS} = 10 \text{ V}$ . The maximum current density ( $I_{\rm DS}$ ) is  $\sim 140 \text{ mA mm}^{-1}$  at  $V_{\rm DS} = 10 \text{ V}$ , while the device demonstrates good pinch-off characteristics with an  $I_{\rm ON}/I_{\rm OFF}$  greater than  $10^8$ . An excellent subthreshold swing of 121 mV dec $^{-1}$

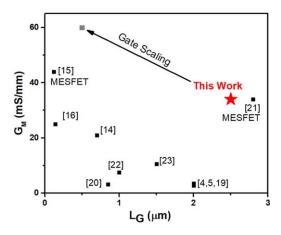

Fig. 3. (Color online)  $G_M$  versus  $L_G$  Benchmarking of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs from this work (red), historical (black) and a projection applying this process with sub- $\mu$ m gate scaling (gray).

was extracted from the log  $I_{\rm DS}-V_{\rm GS}$  curve in Fig. 2(b) which is indicative of the strong channel control expected from a large  $L_G$  and ultra-thin MOSFET channel. Additionally, no adverse effects of implant activation on gate leakage were observed at  $-10\,\rm V$  gate bias [see Fig. 2(b)]. The output family of curves is displayed in Fig. 2(c) obtained over a range of  $V_{\rm GS}$  from +4 to  $-2\,\rm V$  including an on-resistance  $(R_{\rm ON})$  of  $30\,\Omega$  mm at  $V_{\rm GS}=4\,\rm V$  calculated from a linear fit at small  $V_{\rm DS}$ . The  $R_{\rm ON}$  near the ideal flat-band voltage  $(V_G=0)$  was calculated with a series resistance model based on the sum of contact resistance  $(R_C)$ , access resistance  $(R_{\rm access})$ , channel resistance  $(R_{\rm channel})$ , and drift region  $(R_{\rm drift})$  to be  $\sim 73\,\Omega$  mm which is in good agreement with  $\sim 70\,\Omega$  mm extracted from the model and measurement in Fig. 2(c).

The modeled results in Figs. 2(a)–2(c) (solid lines) were constructed by solving the drift-diffusion electron transport equation in ISE Sentaurus Device of the same SAG MOSFET. The model uses dimensions extracted from TEM measurements, as well as material properties ( $n_{\rm sh}$ ,  $\mu$ ,  $R_{\rm sh}$ ) from the measured device or nearest test structure. The Al<sub>2</sub>O<sub>3</sub> thickness was also extracted from the HR-TEM image, and the dielectric constant was assumed to be 9.6. The model is in excellent agreement with the measured results with only some deviation at forward gate bias. The discrepancy is likely due to ideal assumptions concerning electron accumulation, channel doping uniformity, and trapping effects. Thermal effects were not considered but are expected to have an impact at higher  $V_{\rm DS}$  and  $V_G$  bias and especially for an aggressively scaled device (e.g. where dissipated power is greater). Modeling of the same device with  $L_G = 0.5 \,\mu\mathrm{m}$  is included (gray) here to observe the benefits of  $L_G$  scaling under the assumption that temperature will be effectively managed, such as by pulsed operation. With a reduced gate length, a significant improvement in  $G_M$ ,  $I_{DS}$ , and  $R_{ON}$  to 60 mS mm<sup>-1</sup>, 350 mA mm<sup>-1</sup> and 17  $\Omega$  mm respectively, is expected. This illustrates the potential for future highperformance Ga<sub>2</sub>O<sub>3</sub> devices with deep sub-micron gate length and vertically scaled epitaxial device designs.

Benchmarking of these results in Fig. 3 shows a plot of  $G_M$  versus  $L_G$  for SAG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs in this work compared to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices reported in the literature. With the exception of vertically scaled delta-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MESFETs, the  $G_M$  results are state-of-the-art and achieved with a large

gate length. Significant improvements are expected with deep sub-micron gate length scaling following the  $G_{M,\text{ext}} \approx v_{\text{ext}} \cdot C_{\text{GS}}/L_G$  relationship where  $v_{\text{ext}}$  and  $C_{\text{GS}}$  are extrinsic electron velocity and gate–source capacitance, respectively. Further reduction in access resistance can occur by optimizing implant sheet and contact resistance. For example, in our reported MOSFET, the implant  $R_{\text{SH}}$  accounts for approximately 15% of the total device resistance.

We have presented the first SAG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET using a refractory metal gate-first design with Si ion-implantation. The SAG process eliminates source access resistance with among the highest  $G_M$  values reported for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs. The data was compared with a physics-based device simulation which shows strong agreement with the measured results. Additionally, the potential of this process was shown via a device model with gate scaling applied. The SAG process will be essential for future  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device engineering to achieve high-performance, ultra-low power loss devices.

**Acknowledgments** The authors would like to acknowledge the Air Force Office of Scientific Research (AFOSR), who supported this work under grant FA9550-17-1-0279.

ORCID iDs Kyle J. Liddy (1) https://orcid.org/0000-0003-4412-7073

- M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates," Appl. Phys. Lett. 100, 1 (2012).

- 2) M. Higashiwaki, K. Sasaki, T. Kamimura, M. H. Wong, D. Krishnamurthy, A. Kuramata, T. Masui, and S. Yamakoshi, "Depletion-mode Ga<sub>2</sub>O<sub>3</sub> metaloxide-semiconductor field-effect transistors on β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates and temperature dependence of their device characteristics," Appl. Phys. Lett. 103, 1 (2013).

- B. J. Baliga, "Semiconductors for high-voltage, vertical channel field-effect transistors," J. Appl. Phys. 53, 1759 (1982).

- A. Green et al., "3.8 MV cm<sup>-1</sup> breakdown strength of MOVPE-Grown Sndoped β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs," IEEE Electron Device Lett. 37, 902 (2016).

- 5) M. H. Wong, K. Sasaki, A. Kuramata, S. Tamakoshi, and M. Higashiwaki, "Field-Plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs with a breakdown voltage of over 750 V," IEEE Electron Device Lett. 37, 212 (2016).

- 6) K. Zeng, A. Vaidya, and U. Singisetti, "1.85 kV breakdown voltage in lateral field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETS," Electron Device Lett. 39, 1385 (2018).

- C. Joishi et al., "Breakdown Characteristics of β-(Al<sub>0.22</sub>Ga<sub>0.78</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> field-plated modulation-doped field-effect transistors," IEEE Electron Device Lett. 40, 1241 (2019).

- 8) K. Tetzner et al., "Lateral 1.8 kV β-Ga<sub>2</sub>O<sub>3</sub> MOSFET With 155 MW cm<sup>-2</sup> power figure of merit," IEEE Electron Device Lett. 40, 1503 (2019).

- J. K. Mun, K. Cho, W. Chang, H.-W. Jung, and J. Do (ed.) "Editors' Choice—2.32 kV breakdown voltage lateral β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs with source-connected field plate," ECS J. Solid State Sci. Technol. 8, Q3079 (2019).

- 10) K. Chabak et al., "Enhancement-Mode Ga<sub>2</sub>O<sub>3</sub> Wrap-Gate Fin field-effect-transistors on Native (100) β-Ga<sub>2</sub>O<sub>3</sub> substrate with high breakdown voltage," Appl. Phys. Lett. 109, 213501 (2016).

- 11) Z. Hu, K. Nomoto, W. Li, N. Tanen, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H. G. Xing, "Enhancement-mode Ga<sub>2</sub>O<sub>3</sub> vertical transistors with breakdown voltage >1 kV," Electron Device Lett. 39, 869 (2018).

- 12) E. O. Johnson, "Physical limitations on frequency and power parameters of transistors," RCA Rev. 26, 163 (1965).

- 13) K. Ghosh and U. Singisetti, "Ab initio velocity-field curves in monoclinic β-Ga<sub>2</sub>O<sub>3</sub>," J. Appl. Phys. 122, 035702-1 (2017).

- 14) A. J. Green et al., "β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs for radio frequency operation," Electron Device Lett. 38, 790 (2017).

- 15) Z. Xia et al., "β-Ga<sub>2</sub>O<sub>3</sub> delta-doped field-effect transistors with current gain cutoff frequency of 27 GHz," Electron Device Lett. 40, 1052 (2019).

- 16) K. D. Chabak, D. E. Walker, A. J. Green, A. Crespo, M. Lindquist, K. Leedy, S. Tetlak, R. Gilbert, N. A. Moser, and G. Jessen, "Sub-micron gallium oxide radio frequency field-effect transistors," IEEE MTT-S Int. Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications, Conf. paper, 2018.

- 17) K. J. Liddy et al., "Self-aligned gate thin-channel β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs," Conf. paper, 77th Device Research Conf., 2019.

- 18) M. Baldini, Z. Galazka, and G. Wagner, "Recent progress in the growth of β-Ga<sub>2</sub>O<sub>3</sub> for power electronics applications," Mater. Sci. Semicond. Process. 78, 132 (2018).

- 19) H. Dong et al., "Fast switching β-Ga<sub>2</sub>O<sub>3</sub> power MOSFET with a trench-gate structure," Electron Device Lett. (2019), early access article.

- 20) H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Y. Peide, and D. Ye, "High-performance depletion/enhancement-mode β-Ga<sub>2</sub>O<sub>3</sub> on insulator (GOOI)

- field-effect transistors with record drain currents of 600/450 mA mm<sup>-1</sup>," Electron Device Lett. **38**, 103 (2017).

- 21) Z. Xia, C. Joishi, S. Krishnamoorthy, S. Bajaj, Y. Zhang, M. Brenner, S. Lodha, and S. Rajan, "Delta doped β-Ga<sub>2</sub>O<sub>3</sub> field effect transistors with regrown ohmic contacts," Electron Device Lett. 39, 568 (2018).

- 22) K. D. Chabak et al., "Recessed-gate enhancement-mode β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs," Electron Device Lett. 39, 67 (2018).

- 23) Y. Lv et al., "Source-Field-Plated β-Ga<sub>2</sub>O<sub>3</sub> MOSFET with record power figure of merit of 50.4 MW cm<sup>-2</sup>," Electron Device Lett. 40, 83 (2019).