## LETTER • OPEN ACCESS

Design and formation of SiC (0001)/SiO $_2$  interfaces via Si deposition followed by low-temperature oxidation and high-temperature nitridation

To cite this article: Takuma Kobayashi et al 2020 Appl. Phys. Express 13 091003

View the article online for updates and enhancements.

## You may also like

- <u>Barrier height tuning by inverse sputter</u> etching at poly-Si/4H-SiC heterojunction diodes F Triendl, G Pfusterschmied, S Schwarz et

F Triendl, G Pfusterschmied, S Schwarz et al.

- Deposition-Free Process on Reactor Sidewalls during Si Deposition in Vertical Rotating Disk Reactors Soichiro Makino, Kenji Nakashima and Masahide Inagaki

- Epitaxial growth of silicene on ultra-thin Ag(111) films

Junki Sone, Tsuyoshi Yamagami, Yuki Aoki et al.

https://doi.org/10.35848/1882-0786/ababed

## Design and formation of SiC (0001)/SiO<sub>2</sub> interfaces via Si deposition followed by low-temperature oxidation and high-temperature nitridation

Check for updates

LETTER

Takuma Kobayashi<sup>1,2\*†</sup>, Takafumi Okuda<sup>1†</sup>, Keita Tachiki<sup>1</sup>, Koji Ito<sup>1</sup>, Yu-ichiro Matsushita<sup>2</sup>, and Tsunenobu Kimoto<sup>1</sup>

<sup>1</sup>Department of Electronic Science and Engineering, Kyoto University, Nishikyo, Kyoto 615-8510, Japan

<sup>2</sup>Laboratory for Materials and Structures, Institute of Innovative Research, Tokyo Institute of Technology, Yokohama 226-8503, Japan

\*E-mail: kobayashi.t.cp@msl.titech.ac.jp

<sup>†</sup>These authors contributed equally to this work.

Received June 24, 2020; revised July 22, 2020; accepted August 3, 2020; published online August 14, 2020

We report an effective approach to reduce defects at a SiC/SiO<sub>2</sub> interface. Since oxidation of SiC may inevitably lead to defect creation, the idea is to form the interface without oxidizing SiC. Our method consists of four steps: (i) H<sub>2</sub> etching of SiC, (ii) Si deposition, (iii) low-temperature ( $\sim$ 750 °C) oxidation of Si to form SiO<sub>2</sub>, and (iv) high-temperature ( $\sim$ 1600 °C) N<sub>2</sub> annealing to introduce nitrogen atoms. The interface state density estimated by a high (1 MHz)–low method is in the order of 10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup>, two orders of magnitude lower than that of an interface formed by SiC oxidation. © 2020 The Japan Society of Applied Physics

evelopment of high-efficiency power devices is indispensable for meeting the growing requirements of power consumptions and for realizing a sustainable society. In this perspective, silicon carbide (SiC) has been widely accepted as an alternative to silicon (Si) because of its unique material properties (i.e. wide bandgap, high critical electric field, and high thermal conductivity).<sup>1,2)</sup> In particular, SiC metal-oxide-semiconductor field effect transistors (MOSFETs) are promising for low-loss and fast power switches.<sup>1-3)</sup> The performance of MOSFETs is nevertheless limited by the quality of SiC/silicon dioxide (SiO<sub>2</sub>) interfaces; the interface state density  $(D_{\rm IT})$  at SiC/SiO<sub>2</sub> interfaces near the conduction band edge ( $E_{\rm C}$ ) of SiC ( $10^{12}$ – $10^{13}$  eV<sup>-1</sup> cm<sup>-2</sup>) is at least two orders of magnitude higher than that of typical Si/SiO<sub>2</sub> systems  $(\sim 10^{10} \text{ eV}^{-1} \text{ cm}^{-2})^{4,5)}$  A significant portion of electrons at the inversion layer of MOSFETs are thereby trapped by the interface states, resulting in low effective channel mobility  $(\mu_{\rm CH}).^{6-8)}$

Prior studies have indicated various methods to reduce the  $D_{\rm IT}$  at a SiC/SiO<sub>2</sub> interface. The methods are classified into two groups: methods that rely on impurity incorporation and those do not (i.e. oxidation/annealing only). The former approach includes impurities such as nitrogen (N),<sup>9–12)</sup> phosphorus (P),<sup>13,14)</sup> boron (B),<sup>15)</sup> sodium (Na),<sup>16,17)</sup> and barium (Ba).<sup>18)</sup> Among them, incorporation of N by nitric oxide (NO)<sup>9,10)</sup> or nitrous oxide  $(N_2O)^{11,12}$  annealing has been a standard processing step. By introducing N atoms, the  $D_{\rm IT}$  near  $E_{\rm C}$  is reduced to  $\sim 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$  while not significantly degrading the oxide reliability. However, since the reduction in  $D_{\rm IT}$  is insufficient, it is shown that the carrier trapping effect by the interface states is severe even after proper NO annealing.<sup>8)</sup> Although remarkable increase in the  $\mu_{CH}$  (>80 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) is reported for other impurities (i.e. P, B, Na, and Ba), there remains a concern on the oxide reliability. For instance, incorporation of P, Na, and Ba leads to the generation of oxide traps,<sup>19)</sup> threshold voltage instability,<sup>16)</sup> and degradation in the insulating property,<sup>20)</sup> respectively. The latter approach involves thin (~15 nm) oxidation with rapid cooling (>600 °C min<sup>-1</sup>),<sup>21)</sup> high-temperature oxidation (>1400 °C),<sup>22,23)</sup> and post-oxidation annealing in low-oxygen-partial-pressure

ambient at high-temperature (~1500 °C).<sup>24)</sup> Although reduction in  $D_{\rm IT}$  is achieved by these methods, a high-mobility MOSFET is not reported so far. These facts indicate a reasonable hypothesis that the oxidation of SiC inevitably leads to degradation of interface properties via introduction of carbon defects<sup>4,25–27)</sup> and/or fluctuations in the conduction band.<sup>28–30)</sup>

In this paper, we present an alternative pathway to reduce defects at SiC (0001)/SiO<sub>2</sub> interfaces. To avoid the oxidationinduced interface degradation, the idea is to form SiC/SiO<sub>2</sub> structures without oxidizing SiC. In brief, our method proceeds in four stages: (i) hydrogen (H<sub>2</sub>) etching of a SiC surface, (ii) Si deposition, (iii) low-temperature ( $\sim$ 750 °C) oxidation of Si, and (iv) high-temperature ( $\sim$ 1600 °C) nitrogen (N<sub>2</sub>) annealing. A SiC/SiO<sub>2</sub> interface with substantially low *D*<sub>IT</sub> is obtained in this manner. Based on the results, we offer guidelines to form high-quality SiC/SiO<sub>2</sub> interfaces.

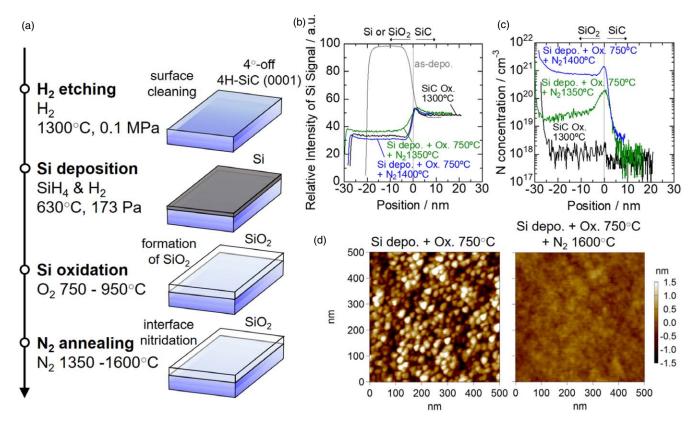

The process flow of gate oxide formation is summarized in Fig. 1(a). We start with  $4^{\circ}$ -off-axis *n*-type SiC (0001) epilayers with a donor density of  $10^{15}$ - $10^{16}$  cm<sup>-3</sup>. After cleaning the samples by the standard RCA procedure, H<sub>2</sub> etching of the samples' surface was performed under 0.1 MPa at 1300 °C for 3 min. Afterward, Si was deposited on the surface by introducing silane (SiH<sub>4</sub>) and H<sub>2</sub>, without exposing the surface to the air. The deposition was carried out under 173 Pa at 630 °C for 1.5 min, resulting in a Si thickness of typically 19–26 nm. Finally, we oxidized the samples either at 750 °C for 24 h or at 950 °C for 12 h and subsequently annealed the samples in N<sub>2</sub> at 1350 °C for 4 h, at 1400 °C for 45 min, or at 1600 °C for 1 min. To investigate the impact of post-oxidation treatment, we also prepared a sample where NO (10% diluted in  $N_2$ ) annealing at 1250 °C for 70 min was performed instead of N<sub>2</sub> annealing. Besides, samples formed by oxidation of SiC were prepared; i.e. as-oxidized SiC samples and those followed by  $NO^{(9,10)}$  or N<sub>2</sub> annealing.<sup>31,32)</sup> H<sub>2</sub> etching was not performed for these thermally-oxidized SiC samples. The equivalent oxide thickness  $(t_{OX})$  of the samples was in the range of 26-44 nm. For MOS structures, we employed circular aluminum (Al) electrodes with a diameter of about 300–500  $\mu$ m.

First, we focus on the structural properties of samples formed by the proposed method. Figure 1(b) depicts the

**Fig. 1.** (Color online) (a) Schematic process flow of forming SiC/SiO<sub>2</sub> structures in the present study. The conditions (i.e. temperature and pressure) and roles of each process are described in the figure. (b) SIMS profiles of Si signal intensity for SiC/SiO<sub>2</sub> and SiC/Si structures. The data were shifted along the *x*-axis so that the interface of SiC and SiO<sub>2</sub> (or Si) is located at the position "0 nm". (c) SIMS profiles of N concentrations for SiC/SiO<sub>2</sub> structures. The data were shifted along the *x*-axis in the same manner as in (b). The sharp increase in the N concentrations observed near the outermost SiO<sub>2</sub> surfaces is likely an artifact of SIMS measurements. (d) Surface morphology of SiC/SiO<sub>2</sub> structures in an area of  $500 \times 500 \text{ nm}^2$  obtained by atomic force microscopy.

secondary ion mass spectrometry (SIMS) profiles of Si signal intensity for SiC/Si and SiC/SiO<sub>2</sub> structures. With Si deposition, a layer with high Si intensity (thickness  $\sim 20$  nm) is indeed formed on the top of SiC. After subsequent oxidation and N<sub>2</sub> annealing, the Si intensity profiles become identical to that of an as-oxidized SiC sample, indicating that the deposited Si is converted into SiO2. Here, the position of SiC/SiO<sub>2</sub> interfaces was determined as the point where carbon (C) signal intensity approximately becomes half of that in SiC. Even when the interface positions were defined based on oxygen (O) intensity, the positions hardly changed (within  $\sim 0.6$  nm). Thus, at least within the accuracy of SIMS measurements, the deposited Si is completely oxidized with the oxidation at 750 °C for 24 h. Figure 1(c) depicts the N concentration profiles of SiC/SiO2 samples measured by SIMS. With N<sub>2</sub> annealing, N atoms are distributed in the oxide, pilling up at the interface of SiC and SiO<sub>2</sub>. The N concentration increases by elevating the temperature of  $N_2$ annealing and reaches  $10^{21}$  cm<sup>-3</sup> after annealing at 1400 °C. In this way, N atoms are introduced at the interface without proceeding the oxidation of SiC. Figure 1(d) shows typical atomic force microscope images for samples after oxidation (750 °C) and that followed by  $N_2$  annealing (1600 °C). The root mean square surface roughness of samples before and after  $N_2$  annealing is estimated as 0.7 nm and 0.2 nm, respectively. A rather smooth SiO<sub>2</sub> surface is eventually obtained, owing to the structure reconstruction of SiO<sub>2</sub> during high-temperature N<sub>2</sub> annealing.

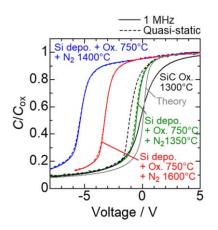

We now focus on the electric characteristics of MOS structures. The quasi-static and 1 MHz capacitance-voltage

(*C–V*) characteristics of the MOS structures are shown in Fig. 2. Large frequency dispersion observed for the asoxidized SiC sample is significantly reduced in samples formed by the proposed method, implying a strong reduction in the  $D_{\rm TT}$ . Meanwhile, negative flat band voltage shifts are observed for the samples formed by the present method, corresponding to the effective fixed charge density of  $+3.9 \times 10^{11}$ ,  $+3.1 \times 10^{12}$ , and  $+2.3 \times 10^{12}$  cm<sup>-2</sup> for samples annealed in N<sub>2</sub> at 1350 °C, 1400 °C, and 1600 °C, respectively. Since more N atoms are introduced into the oxide with N<sub>2</sub> annealing at higher temperature [Fig. 1(c)], the

**Fig. 2.** (Color online) Quasi-static and 1 MHz C-V characteristics of SiC MOS structures. Theoretical deep-depletion capacitance<sup>33,34)</sup> assuming a donor density of 10<sup>16</sup> cm<sup>-3</sup> and oxide thickness of 30 nm is also shown for comparison. The capacitance values were normalized by the oxide capacitance ( $C_{\text{OX}}$ ).

positive charge likely originates from the incorporated N atoms.

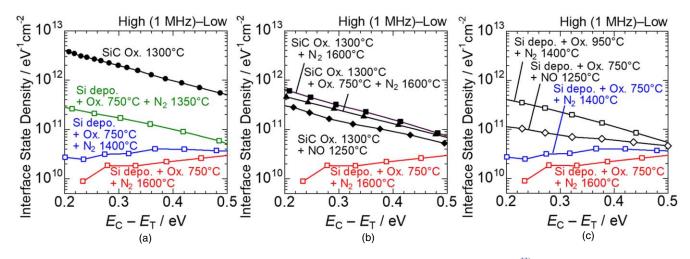

For a quantitative discussion, the energy distributions of  $D_{\rm IT}$  were estimated by a high (1 MHz) –low method.<sup>33)</sup> The results are summarized in Figs. 3(a)-3(c). First we investigate the impact of  $N_2$  annealing temperature in Fig. 3(a), where the result for an as-oxidized SiC sample is also shown for comparison. As expected from the C-V characteristics (Fig. 2), the samples prepared by the present method exhibit lower  $D_{\rm IT}$  than that formed by oxidation of SiC. The  $D_{\rm IT}$  is effectively reduced when increasing the temperature of N2 annealing; e.g. the  $D_{\text{IT}}$  values at  $E_{\text{C}}$  -0.3 eV are about  $1.7 \times 10^{11}$ ,  $3.2 \times 10^{10}$ , and  $1.8 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$  [possible error:  $\pm\,(2\text{--}3)\times10^{10}\,\text{eV}^{-1}\,\text{cm}^{-2}]$  for samples annealed at 1350 °C, 1400 °C, and 1600 °C, respectively. Although the role of H<sub>2</sub> etching is uncertain, N<sub>2</sub> annealing plays the key role in obtaining low  $D_{\rm IT}$ ; high-temperature N<sub>2</sub> annealing should be performed to introduce sufficient N atoms at the interface [Fig. 1(c)].

In Fig. 3(b), we compare the obtained  $D_{\rm IT}$  with samples formed by thermal oxidation of SiC. As a result, the  $D_{\rm IT}$ values near the  $E_{\rm C}$  (e.g.  $E_{\rm C}$  –0.3 eV) for a sample obtained by the proposed method is about ten times lower than that formed by typical methods; i.e. oxidation of SiC followed by  $NO^{9,10}$  or  $N_2$  annealing.<sup>31,32</sup> Furthermore, it is confirmed that low-temperature oxidation (750  $^{\circ}\text{C})$  followed by  $N_2$ annealing (1600 °C) has a limited effect on a sample formed by oxidation of SiC. Since oxidation of SiC leads to the generation of defects that cannot be easily passivated, the deposition of Si is a vital step towards reducing the  $D_{\rm IT}$ . A clearer evidence is observed in Fig. 3(c), where the impacts of Si oxidation temperature and post-oxidation treatment are investigated. When we increase the oxidation temperature of Si up to 950 °C, by which not only the deposited Si but also the SiC beneath it might be slightly oxidized, considerable increase in the  $D_{\rm IT}$  is observed. Thus, low oxidation temperature ( $\sim$ 750 °C) is necessary to guarantee that the oxidation of SiC does not take place. For oxidation at 750 °C for 24 h, we indeed confirmed that even a bare SiC sample was hardly oxidized. Although SiC/SiO<sub>2</sub> structures were also formed by Si deposition and subsequent oxidation in a previous study, the oxidation temperature there was rather high (1100 °C).<sup>35)</sup> In such a case, it is likely that not only the deposited Si but also SiC is oxidized. As shown in Fig. 3(c), the post-oxidation treatment is also particularly important; when the annealing is performed in NO instead of N<sub>2</sub>, the  $D_{\text{IT}}$  increases due to additional SiC oxidation during NO annealing. After all, the process condition has to be carefully designed so as to oxidize Si but not SiC.

Here we discuss the cause of the observed defect passivation upon N<sub>2</sub> annealing. The role of N atoms has been extensively discussed in literature; e.g. passivation of carbon defects, <sup>9,36–39)</sup> suboxide bonds, <sup>36,38)</sup> and dangling bonds at/ near a SiC/SiO<sub>2</sub> interface.<sup>9)</sup> Since we avoided oxidation of SiC, the generation of carbon defects should be suppressed. Passivation of carbon defects are thereby unlikely in our case. In contrast, the passivation of suboxide bonds and/or dangling bonds might be plausible. Indeed, a theoretical study suggested that Si-Si bonds (with various length) in near-interface  $SiO_2$  form antibonding levels near the  $E_C$  of SiC, which could be passivated by N atoms.<sup>38)</sup> Studies based on X-ray photoelectron spectroscopy have indicated Si≡N bonds in SiC/SiO<sub>2</sub> structure prepared by NO<sup>9,39)</sup> or N<sub>2</sub><sup>40)</sup> annealing, suggesting that Si dangling bonds could also be passivated by N atoms.9) Hence, we speculate that hightemperature N<sub>2</sub> annealing lets the interface structure to reconstruct and passivates the suboxide bonds and dangling bonds at/near the interface, leading to the significant reduction in  $D_{\text{IT}}$  [Fig. 3(a)].

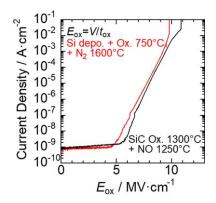

Finally, we characterized the reliability of an oxide obtained by proposed method. As shown in Fig. 4, the time-zero-breakdown field of the sample was estimated as 9.8 MVcm<sup>-1</sup>, only slightly degraded compared to that formed by NO annealing (10.9 MV cm<sup>-1</sup>). As a result of bi-directional 1 MHz *C*–*V* measurement at 200 °C, the hysteresis was negligibly small (<0.1 V) by applying positive (negative) bias stress at +10 V (–10 V), where +10 V corresponds to an oxide field of about +3.3 MVcm<sup>-1</sup>.

In conclusion, we developed an effective method to reduce defects at SiC (0001)/SiO<sub>2</sub> interfaces. The key is to form SiC/SiO<sub>2</sub> structures without oxidizing SiC and to perform high-temperature N<sub>2</sub> annealing afterwards; we deposited Si on SiC and subsequently oxidized the Si at low-temperature ( $\sim$ 750 °C) to form SiO<sub>2</sub>. High-temperature N<sub>2</sub> annealing

**Fig. 3.** (Color online) Energy distribution of  $D_{\text{IT}}$  for SiC MOS structures obtained by a high (1 MHz)-low method;<sup>33)</sup> (a) impact of N<sub>2</sub> annealing temperature, (b) comparison with typical methods (NO and N<sub>2</sub> annealings), and (c) impacts of oxidation temperature and post-oxidation treatment. The possible error in the  $D_{\text{IT}}$  values is estimated as about  $\pm$  (2–3) × 10<sup>10</sup> eV<sup>-1</sup> cm<sup>-2</sup>.

**Fig. 4.** (Color online) Current density–oxide field characteristics of SiC MOS structures. The oxide field ( $E_{OX}$ ) was calculated by dividing the applied gate voltage (V) by the equivalent oxide thickness ( $t_{OX}$ ).

(~1600 °C) was then performed to let the interface structure to reconstruct and to passivate the suboxide bonds and/or dangling bonds by N atoms. In this way, SiC/SiO<sub>2</sub> interface with substantially low defect density (~10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup>) was formed. The time-zero-breakdown field of the oxide was about 9.8 MV cm<sup>-1</sup>, only slightly degraded compared to that formed by NO annealing (10.9 MV cm<sup>-1</sup>).

**Acknowledgments** This work was partly supported by the Open Innovation Platform with Enterprises, Research Institute and Academia (OPERA) Program from the Japan Science and Technology Agency. This work was also partly supported by the Grant-in-Aids for Scientific Research (A) (Grant Nos. 18H03770 and 18H03873) from the Japan Society for the Promotion of Science.

ORCID iDs Takuma Kobayashi D https://orcid.org/0000-0002-2755-5079 Takafumi Okuda D https://orcid.org/0000-0002-0880-595X Keita Tachiki D https://orcid.org/0000-0003-0795-0634 Koji Ito D

https://orcid.org/0000-0002-7229-2722 Yu-ichiro Matsushita ib https://orcid.org/0000-0002-9254-5918 Tsunenobu Kimoto ib https://orcid.org/0000-0002-6649-2090

- T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology (Wiley, Singapore, 2014).

- 2) H. Matsunami and T. Kimoto, Mater. Sci. Eng. R 20, 125 (1997).

- 3) B. J. Baliga, IEEE Electron Device Lett. 10, 455 (1989).

- V. V. Afanasev, M. Bassler, G. Pensl, and M. Schulz, Phys. Status Solidi A 162, 321 (1997).

- N. S. Saks, S. S. Mani, and A. K. Agarwal, Appl. Phys. Lett. 76, 2250 (2000).

- 6) E. Arnold and D. Alok, IEEE Trans. Electron Devices 48, 1870 (2001).

- H. Yoshioka, J. Senzaki, A. Shimozato, Y. Tanaka, and H. Okumura, AIP Adv. 5, 017109 (2015).

- T. Hatakeyama, Y. Kiuchi, M. Sometani, S. Harada, D. Okamoto, H. Yano, Y. Yonezawa, and H. Okumura, Appl. Phys. Express 10, 046601 (2019).

- 9) P. Jamet, S. Dimitrijev, and P. Tanner, J. Appl. Phys. 90, 5058 (2001).

- 10) G. Y. Chung et al., IEEE Electron Device Lett. 22, 176 (2001).

- 11) L. A. Lipkin, M. K. Das, and J. W. Palmour, Mater. Sci. Forum 389–393, 985 (2002).

- 12) T. Kimoto, Y. Kanzaki, M. Noborio, H. Kawano, and H. Matsunami, Jpn. J. Appl. Phys. 44, 1213 (2005).

- 13) D. Okamoto, H. Yano, T. Hatayama, and T. Fuyuki, Appl. Phys. Lett. 96, 203508 (2010).

- 14) D. Okamoto, H. Yano, K. Hirata, T. Hatayama, and T. Fuyuki, IEEE Electron Device Lett. 31, 710 (2010).

- 15) D. Okamoto, M. Sometani, S. Harada, R. Kosugi, Y. Yonezawa, and H. Yano, IEEE Electron Device Lett. 35, 1176 (2014).

- 16) F. Allerstam, H. Ö. Ólafsson, G. Gudjónsson, D. Dochev,

- E. Ö. Sveinbjörnsson, T. Rödle, and R. Jos, J. Appl. Phys. 101, 124502 (2007).

B. R. Tuttle, S. Dhar, S.-H. Ryu, X. Zhu, J. R. Williams, L. C. Feldman, and

- S. T. Pantelides, J. Appl. Phys. 109, 023702 (2011).

18) D. J. Lichtenwalner, L. Cheng, S. Dhar, A. Agarwal, and J. W. Palmour, Appl. Phys. Lett. 105, 182107 (2014).

- H. Yano, N. Kanafuji, A. Osawa, T. Hatayama, and T. Fuyuki, IEEE Trans. Electron Devices 62, 324 (2015).

- 20) A. Chanthaphan, Y. Katsu, T. Hosoi, T. Shimura, and H. Watanabe, Jpn. J. Appl. Phys. 55, 120303 (2016).

- 21) R. H. Kikuchi and K. Kita, Appl. Phys. Lett. 105, 032106 (2014).

- 22) T. Hosoi, D. Nagai, M. Sometani, Y. Katsu, H. Takeda, T. Shimura, M. Takei, and H. Watanabe, Appl. Phys. Lett. 109, 182114 (2016).

- 23) M. Sometani, D. Nagai, Y. Katsu, T. Hosoi, T. Shimura, M. Takei, Y. Yonezawa, and H. Watanabe, Jpn. J. Appl. Phys. 56, 04CR04 (2017).

- 24) T. Kobayashi, K. Tachiki, K. Ito, and T. Kimoto, Appl. Phys. Express 12, 031001 (2019).

- 25) M. Bassler, G. Pensl, and V. Afanas'ev, Diam. Relat. Mater. 6, 1472 (1997).

- 26) T. Kobayashi and T. Kimoto, Appl. Phys. Lett. 111, 062101 (2017).

- 27) T. Umeda, G.-W. Kim, T. Okuda, M. Sometani, T. Kimoto, and S. Harada, Appl. Phys. Lett. **113**, 061605 (2018).

- 28) H. Yoshioka and K. Hirata, AIP Adv. 8, 045217 (2018).

- 29) Y. Matsushita and A. Oshiyama, Nano Lett. 17, 6458 (2017).

- 30) K. Ito, T. Kobayashi, and T. Kimoto, (2019), arXiv:1904.08574.

- A. Chanthaphan, T. Hosoi, T. Shimura, and H. Watanabe, AIP Adv. 5, 097134 (2015).

- 32) K. Tachiki and T. Kimoto, Ext. Abst. of Int. Conf. on Silicon Carbide and Related Materials 2019, 2019 Mo-2A-05.

- 33) E. H. Nicollian and J. R. Brews, *MOS Physics and Technology* (Wiley, New York, 1982).

- 34) H. Yoshioka, T. Nakamura, and T. Kimoto, J. Appl. Phys. 111, 014502 (2012).

- 35) R. Pascu, C. Romanitan, P. Varasteanu, and M. Kusko, IEEE J. Electron Devices Soc. 7, 158 (2018).

- 36) V. V. Afanas'ev, A. Stesmans, F. Ciobanu, G. Pensl, K. Y. Cheong, and S. Dimitrijev, Appl. Phys. Lett. 82, 568 (2003).

- 37) P. Deák, J. M. Knaup, T. Hornos, C. Thill, A. Gali, and T. Frauenheim, J. Phys. D: Appl. Phys. 40, 6242 (2007).

- 38) S. Wang, S. Dhar, S. Wang, A. C. Ahyi, A. Franceschetti, J. R. Williams, L. C. Feldman, and S. T. Pantelides, Phys. Rev. Lett. 98, 026101 (2007).

- 39) H. Li, S. Dimitrijev, D. Sweatman, H. B. Harrison, P. Tanner, and B. Feil, J. Appl. Phys. 86, 4316 (1999).

- 40) S. Asaba, T. Ito, S. Fukatsu, Y. Nakabayashi, T. Shimizu, M. Furukawa, T. Suzuki, and R. Iijima, Proc. 31st Int. Symp. on Power Semiconductor Devices & ICs, 2019, p. 139.