Abstract

To improve mobility of fabricated silicon metal-oxide–semiconductor (MOS) quantum devices, forming gas annealing is a common method used to mitigate the effects of disorder at the Si/SiO2 interface. However, the importance of activation annealing is usually ignored. Here, we show that a high vacuum environment for implantation activation is beneficial for improving mobility compared to nitrogen atmosphere. Low-temperature transport measurements of Hall bars show that peak mobility can be improved by a factor of two, reaching  using high vacuum annealing during implantation activation. Moreover, the charge stability diagram of a single quantum dot is mapped, with no visible disturbance caused by disorder, suggesting the possibility of fabricating high-quality quantum dots on commercial wafers. Our results may provide valuable insights into device optimization in silicon-based quantum computing.

using high vacuum annealing during implantation activation. Moreover, the charge stability diagram of a single quantum dot is mapped, with no visible disturbance caused by disorder, suggesting the possibility of fabricating high-quality quantum dots on commercial wafers. Our results may provide valuable insights into device optimization in silicon-based quantum computing.

Export citation and abstract BibTeX RIS

With rapid development of silicon quantum devices, quantum dots fabricated on silicon have become one of the most promising candidates for quantum computing [1]. In particular, employing nuclear spin-free 28Si [2], which is abundant in natural silicon, this kind of structure enables high fidelity control of spin qubits by offering long coherence times [3–7]. High-quality silicon-based material is necessary for the implementation of fault-tolerant quantum computing [8,9]. As silicon metal-oxide semiconductors (MOS) are widely used in commercial electronic devices, specifically for their stable performances [10], leveraging complementary MOS (CMOS) technology to scale up spin-qubit manipulations is an alternative solution. Possible applications of commercial MOS technology in the field of spin qubits have been identified [11,12]. Therefore, using commercial silicon wafers to fabricate high-quality quantum dots is an important issue.

As a metric for assessing the quality of the semiconductor/oxide interface, high mobility indicates low disorder and material uniformity at the confining interfaces. Quantum dots for spin qubits usually operate at a low density, where the disorder and material uniformity affect the electrical property significantly. The increasing of the mobility suggests an enhancement of the quality of silicon wafers, which is beneficial for obtaining reproducible quantum dots [13]. Early studies on Si MOS show the results of quantum dot devices with relative low-mobility wafers [14,15]. For example, a gate-defined quantum dot has been achieved in intrinsic silicon with the mobility of  [16]. Researchers are trying to further improve electron mobility by reducing defect at the SiO2/Si interface. A recent research shows a peak mobility of

[16]. Researchers are trying to further improve electron mobility by reducing defect at the SiO2/Si interface. A recent research shows a peak mobility of  which can be extended to

which can be extended to  by forming gas annealing [17]. To determine the dominant sources of disorder in Si MOS devices, investigations on the magneto-transport of Hall bars of these structures were performed [18–20]. By analysing the mobility

by forming gas annealing [17]. To determine the dominant sources of disorder in Si MOS devices, investigations on the magneto-transport of Hall bars of these structures were performed [18–20]. By analysing the mobility  as a function of density (n) and quantum lifetime

as a function of density (n) and quantum lifetime  , the dominant source limiting mobility was identified [21]. Similar experiments were performed on GaAs/AlGaAs heterostructure [22–24], Si MOSFET [25], and Si/SiGe heterostructure [26–28]. Based on these findings, several means to reduce disorder to improve mobility in Si MOS structures were found, including using strained silicon and annealing samples in N2 environments [29,30].

, the dominant source limiting mobility was identified [21]. Similar experiments were performed on GaAs/AlGaAs heterostructure [22–24], Si MOSFET [25], and Si/SiGe heterostructure [26–28]. Based on these findings, several means to reduce disorder to improve mobility in Si MOS structures were found, including using strained silicon and annealing samples in N2 environments [29,30].

In this letter, we study silicon MOS Hall bars fabricated using commercial silicon wafers with different activation environments and growth methods. We obtain a peak mobility of  , along with a critical electron density of

, along with a critical electron density of  , in a commercial silicon wafer by using high vacuum annealing during implantation activation in addition to forming gas annealing. The mobility of two-dimensional electron gas (2DEG) is increased by a factor of two by using activation annealing in high vacuum rather than in nitrogen atmosphere. We find that the dominant scattering mechanism that limits the peak mobility is short-range scattering, and the effect of phonon scattering can be ignored below 1.5 K. Furthermore, a single quantum dot is fabricated to demonstrate the possibility of producing high-quality quantum dots using wafers with the improved mobility.

, in a commercial silicon wafer by using high vacuum annealing during implantation activation in addition to forming gas annealing. The mobility of two-dimensional electron gas (2DEG) is increased by a factor of two by using activation annealing in high vacuum rather than in nitrogen atmosphere. We find that the dominant scattering mechanism that limits the peak mobility is short-range scattering, and the effect of phonon scattering can be ignored below 1.5 K. Furthermore, a single quantum dot is fabricated to demonstrate the possibility of producing high-quality quantum dots using wafers with the improved mobility.

The Hall bars and quantum dots devices are fabricated on 8 inch commercial silicon wafers. The wafers consist of a 10 nm SiO2 cap layer formed by thermal oxidation and a  Si substrate. All batches of samples are fabricated using the same process steps except for different annealing conditions. The standard fabrication process for sample preparation is as follows: ion implantation (phosphorus) with a dose of

Si substrate. All batches of samples are fabricated using the same process steps except for different annealing conditions. The standard fabrication process for sample preparation is as follows: ion implantation (phosphorus) with a dose of  ; application of an annealing process for ion activation at the temperature of

; application of an annealing process for ion activation at the temperature of  in either high vacuum

in either high vacuum  or N2 atmosphere; fabrication of Ohmic contact regions using buffered oxide etching and evaporation of Ti/Au; and deposition of 30 nm thick aluminium oxide (Al2O3) as gate insulator at the temperature of

or N2 atmosphere; fabrication of Ohmic contact regions using buffered oxide etching and evaporation of Ti/Au; and deposition of 30 nm thick aluminium oxide (Al2O3) as gate insulator at the temperature of  . After that, a layer of Al above the Al2O3 is added to define the conductive channel. A final annealing with forming gas (15% H2 and 85% N2) for 30 min at the temperature of

. After that, a layer of Al above the Al2O3 is added to define the conductive channel. A final annealing with forming gas (15% H2 and 85% N2) for 30 min at the temperature of  is performed to reduce the defects induced by e-beam lithography and metal evaporation [17,31].

is performed to reduce the defects induced by e-beam lithography and metal evaporation [17,31].

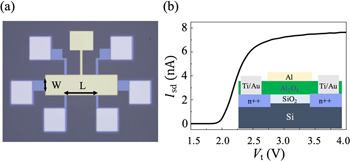

A channel length of  and width of

and width of  are chosen for the Hall bars on commercial silicon wafers (fig. 1(a)). The inset of fig. 1(b) shows a cross-section schematic of the device. The top gate (faint yellow area) is for applying a DC voltage Vt to accumulate the 2DEG at the Si/SiO2 interface to generate a current with a voltage

are chosen for the Hall bars on commercial silicon wafers (fig. 1(a)). The inset of fig. 1(b) shows a cross-section schematic of the device. The top gate (faint yellow area) is for applying a DC voltage Vt to accumulate the 2DEG at the Si/SiO2 interface to generate a current with a voltage  . The standard "turn on" curve of the current (fig. 1(b)) saturates at

. The standard "turn on" curve of the current (fig. 1(b)) saturates at  with a total resistivity of

with a total resistivity of  at 4.2 K.

at 4.2 K.

Fig. 1: (a) Optical micrograph of a Si MOS Hall bar showing the ion implantation region (grey areas) along with Ti/Au pads (white squares) and the top gate (faint yellow area) made of Al. (b) Standard current-voltage curve obtained under a source-drain bias of  . Inset: cross-section of the Si MOS Hall bar device.

. Inset: cross-section of the Si MOS Hall bar device.

Download figure:

Standard imageThen, low-temperature transport measurements are performed at temperatures  in a He-3 refrigerator using an SR830 lock-in amplifier at a frequency of

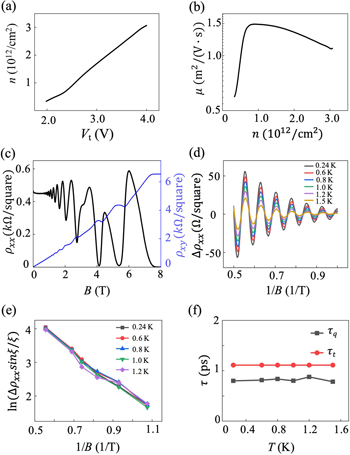

in a He-3 refrigerator using an SR830 lock-in amplifier at a frequency of  to reveal the properties of our devices. In our devices, the density of the 2DEGs shows a linear dependence on the top gate voltage, with a typical curve shown in fig. 2(a). Meanwhile, the mobility of the 2DEGs also changes as the gate voltage varies. The dependence of the mobility

to reveal the properties of our devices. In our devices, the density of the 2DEGs shows a linear dependence on the top gate voltage, with a typical curve shown in fig. 2(a). Meanwhile, the mobility of the 2DEGs also changes as the gate voltage varies. The dependence of the mobility  on the density (n) under different top gate voltages is presented in fig. 2(b). In the low-density

on the density (n) under different top gate voltages is presented in fig. 2(b). In the low-density  regime, the curve roughly follows a

regime, the curve roughly follows a  trend, corresponding to the effect of fixed charges [32]. The mobility decreases when further increasing the density

trend, corresponding to the effect of fixed charges [32]. The mobility decreases when further increasing the density  due to interface roughness scattering at the Si/SiO2 interface [33]. The mobility reaches a peak value of

due to interface roughness scattering at the Si/SiO2 interface [33]. The mobility reaches a peak value of  at a density of

at a density of  .

.

Fig. 2: (a) 2DEG Hall density n's dependency on top gate voltage Vt. (b) Mobility vs. density of device of batch 3 (high vacuum). (c) Longitudinal resistivity ( , black) and transverse resistivity (

, black) and transverse resistivity ( , blue) at

, blue) at  as a function of magnetic field. (d) Fourier spectrum of SdH oscillations from 1 T to 2 T in the temperature range of

as a function of magnetic field. (d) Fourier spectrum of SdH oscillations from 1 T to 2 T in the temperature range of  after subtracting the polynomial background and

after subtracting the polynomial background and  (0). (e) Magnetic field dependence of the logarithm of

(0). (e) Magnetic field dependence of the logarithm of  under different temperatures. (f) Quantum lifetime

under different temperatures. (f) Quantum lifetime  and transport lifetime

and transport lifetime  are independent of temperature.

are independent of temperature.

Download figure:

Standard imageIn fig. 2(c), at the peak mobility, Hall transport measurements are performed by mapping the longitudinal resistivity  and the transverse resistivity

and the transverse resistivity  under different magnetic fields. The onset of magnetic field for Shubnikov-de Hass (SdH) oscillations is 0.7 T (

under different magnetic fields. The onset of magnetic field for Shubnikov-de Hass (SdH) oscillations is 0.7 T ( ). When the magnetic field is above

). When the magnetic field is above  , the transverse resistivity

, the transverse resistivity  shows plateaus with an even filling factor

shows plateaus with an even filling factor  while oscillations of the longitudinal resistivity

while oscillations of the longitudinal resistivity  are observed. The transverse resistivity

are observed. The transverse resistivity  plateaus with odd filling factor are invisible as a result of valley degeneracy. Spins split at a higher magnetic field of

plateaus with odd filling factor are invisible as a result of valley degeneracy. Spins split at a higher magnetic field of  , corresponding to a Zeeman splitting energy of

, corresponding to a Zeeman splitting energy of  , where

, where  is the electronic Lande factor and

is the electronic Lande factor and  is the Bohr magneton.

is the Bohr magneton.

In fig. 2(d), we obtain  as a function of magnetic field (B) from 1 T to 2 T. After subtracting the polynomial background and

as a function of magnetic field (B) from 1 T to 2 T. After subtracting the polynomial background and  (the longitudinal resistivity at zero magnetic field), six oscillations

(the longitudinal resistivity at zero magnetic field), six oscillations  vs. 1/B are plotted under different temperatures. The oscillations show a period of 4 in ν, consistent with two-fold valley degeneracy and two-fold spin degeneracy. The oscillations can be fitted perfectly using the formula [34]

vs. 1/B are plotted under different temperatures. The oscillations show a period of 4 in ν, consistent with two-fold valley degeneracy and two-fold spin degeneracy. The oscillations can be fitted perfectly using the formula [34]

where  is the Dingle factor, where at low field

is the Dingle factor, where at low field  , with

, with  ,

,  is the cyclotron frequency,

is the cyclotron frequency,  is the effective mass, kB is Boltzmann's constant,

is the effective mass, kB is Boltzmann's constant,  is the quantum lifetime of the electrons and ℏ is the reduced Planck constant. When

is the quantum lifetime of the electrons and ℏ is the reduced Planck constant. When  , the extrapolated amplitude for

, the extrapolated amplitude for  in eq. (1) can be used to obtain effective mass

in eq. (1) can be used to obtain effective mass  , which is consistent with the transverse effective mass of silicon in theory.

, which is consistent with the transverse effective mass of silicon in theory.

Figure 2(e) shows  as a function of

as a function of  , from which the quantum lifetime values

, from which the quantum lifetime values  can be extracted. We find that

can be extracted. We find that  is independent of temperature, similar to the transport lifetime

is independent of temperature, similar to the transport lifetime  , as shown in fig. 2(f). We note that this result differs from previous works on Si/SiGe heterostructure [28] and GaAs/AlGaAs heterostructures [24], where phonon scattering was non-negligible. In addition, the value of

, as shown in fig. 2(f). We note that this result differs from previous works on Si/SiGe heterostructure [28] and GaAs/AlGaAs heterostructures [24], where phonon scattering was non-negligible. In addition, the value of  ps implies a Landau-level broadening of

ps implies a Landau-level broadening of  , which is consistent with the reported value of

, which is consistent with the reported value of  [13], giving the upper bound of valley splitting energy in our devices. For comparison, valley splitting energies range from 0.7 to

[13], giving the upper bound of valley splitting energy in our devices. For comparison, valley splitting energies range from 0.7 to  in previous Si MOSFETs [35–38].

in previous Si MOSFETs [35–38].

It is worth noting that the Dingle ratio  almost equals unity, indicating that the dominant scattering mechanism restricting the peak mobility of this sample (fig. 2(f)) is short-range scattering rather than long-range scattering. This result is in accordance with a previous work in which the fixed charges and defects at the SiO2/Al2O3 or SiO2/Si interfaces dominate the scattering [39]. The insensitivity of both

almost equals unity, indicating that the dominant scattering mechanism restricting the peak mobility of this sample (fig. 2(f)) is short-range scattering rather than long-range scattering. This result is in accordance with a previous work in which the fixed charges and defects at the SiO2/Al2O3 or SiO2/Si interfaces dominate the scattering [39]. The insensitivity of both  and

and  to temperature implies that phonon effects are not dominant here even if we cannot rule out other effects that limit the mobility of the wafers [40].

to temperature implies that phonon effects are not dominant here even if we cannot rule out other effects that limit the mobility of the wafers [40].

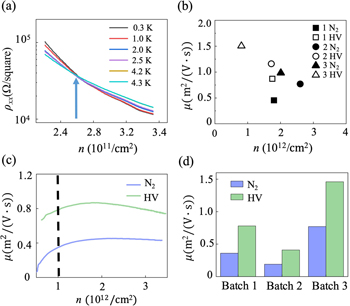

In fig. 3(a), by varying the gate voltage (Vt),  (

( ) as a function of density (n) is obtained. After changing the temperature, these curves feature a stable crossing point at a critical electron density (

) as a function of density (n) is obtained. After changing the temperature, these curves feature a stable crossing point at a critical electron density ( ), which is a signature of metal-insulator transition. The value of nc in our MOS Hall bars is consistent with the previously reported value [41–44]. In fig. 3(b), the peak mobility and density for different parameter settings are listed. Data of hollow symbols are from devices using high vacuum

), which is a signature of metal-insulator transition. The value of nc in our MOS Hall bars is consistent with the previously reported value [41–44]. In fig. 3(b), the peak mobility and density for different parameter settings are listed. Data of hollow symbols are from devices using high vacuum  activation annealing, while those of solid symbols come from devices activated in nitrogen atmosphere. Moreover, different wafers, which can be used for quantum dots fabrication, are introduced to identify if there is any difference between intrinsic substrates (floating zone (FZ) grown wafers) and doped substrates (Czochralski (Cz) grown wafers), even both of them can be used for quantum dots fabrication [45–47]. Batches 1 and 2 are fabricated using Cz wafers, while batch 3 is fabricated with FZ wafers. Cz wafers are slightly boron (B+)-doped with a resistivity of

activation annealing, while those of solid symbols come from devices activated in nitrogen atmosphere. Moreover, different wafers, which can be used for quantum dots fabrication, are introduced to identify if there is any difference between intrinsic substrates (floating zone (FZ) grown wafers) and doped substrates (Czochralski (Cz) grown wafers), even both of them can be used for quantum dots fabrication [45–47]. Batches 1 and 2 are fabricated using Cz wafers, while batch 3 is fabricated with FZ wafers. Cz wafers are slightly boron (B+)-doped with a resistivity of  , whereas FZ wafers are intrinsic and undoped with a resistivity of approximately

, whereas FZ wafers are intrinsic and undoped with a resistivity of approximately  . Comparing those with the same wafer but under different annealing conditions, a higher peak mobility is clearly observed for the ones under high vacuum activation annealing instead of nitrogen atmosphere annealing. A peak mobility up to

. Comparing those with the same wafer but under different annealing conditions, a higher peak mobility is clearly observed for the ones under high vacuum activation annealing instead of nitrogen atmosphere annealing. A peak mobility up to  is obtained for batch 3. Overall, the peak mobility of the 2DEGs fabricated using FZ wafers is higher than that of the 2DEGs fabricated using Cz wafers here. We attribute this trend to fewer donors in FZ wafers than in Cz wafers. Considering dopant atoms, the background doping values of Cz wafers and FZ wafers are approximately

is obtained for batch 3. Overall, the peak mobility of the 2DEGs fabricated using FZ wafers is higher than that of the 2DEGs fabricated using Cz wafers here. We attribute this trend to fewer donors in FZ wafers than in Cz wafers. Considering dopant atoms, the background doping values of Cz wafers and FZ wafers are approximately  and

and  , respectively. For FZ wafers, the possible effects from dopant atoms are relatively small. Additionally, for quantum dots in Si MOS, three kinds of charge transitions are usually considered, namely,

, respectively. For FZ wafers, the possible effects from dopant atoms are relatively small. Additionally, for quantum dots in Si MOS, three kinds of charge transitions are usually considered, namely,  centres, Pb centres, and unintentional quantum dots [39]. For

centres, Pb centres, and unintentional quantum dots [39]. For  centres, the effect is related to the fixed charges, typically arising from the interface between Al2O3 and SiO2. This kind of defect is usually induced by radiation during e-beam evaporation and is usually located further from the quantum well. Such defects could be worsened when implementing e-beam lithography for smaller structures [31]. Another kind of defect, the Pb centre, is formed by a single dangling bond on silicon [48]. Previous experiments have identified that the most common defects of the Pb centre form at the interface between Si and SiO2 [49]. The final annealing with H2 is performed to passivate the Pb centres. Unintentional quantum dots are formed by strains between different materials [50], which is not discussed here. All of the effects would behave as disorders and they usually occur simultaneously. Mitigation of any of these effects will lead to an increase of electron mobility.

centres, the effect is related to the fixed charges, typically arising from the interface between Al2O3 and SiO2. This kind of defect is usually induced by radiation during e-beam evaporation and is usually located further from the quantum well. Such defects could be worsened when implementing e-beam lithography for smaller structures [31]. Another kind of defect, the Pb centre, is formed by a single dangling bond on silicon [48]. Previous experiments have identified that the most common defects of the Pb centre form at the interface between Si and SiO2 [49]. The final annealing with H2 is performed to passivate the Pb centres. Unintentional quantum dots are formed by strains between different materials [50], which is not discussed here. All of the effects would behave as disorders and they usually occur simultaneously. Mitigation of any of these effects will lead to an increase of electron mobility.

Fig. 3: (a) Resistivity  as a function of density n in the temperature range of

as a function of density n in the temperature range of  . (b) Comparison of the peak mobility and density from different batches of devices. Batch 1: Cz silicon wafers with a layer of home-grown silicon oxide. Batch 2: Cz commercial silicon/silicon oxide wafers. Batch 3: FZ commercial silicon/silicon oxide wafers. Data of hollow symbols are from devices whose activation is implemented in a high vacuum (HV) environment, solid symbols correspond to devices activated in nitrogen atmosphere. (c) Electron mobility as a function of density obtained from a device which belongs to batch 1. (d) Comparison of the mobility differences at a density of

. (b) Comparison of the peak mobility and density from different batches of devices. Batch 1: Cz silicon wafers with a layer of home-grown silicon oxide. Batch 2: Cz commercial silicon/silicon oxide wafers. Batch 3: FZ commercial silicon/silicon oxide wafers. Data of hollow symbols are from devices whose activation is implemented in a high vacuum (HV) environment, solid symbols correspond to devices activated in nitrogen atmosphere. (c) Electron mobility as a function of density obtained from a device which belongs to batch 1. (d) Comparison of the mobility differences at a density of  between high vacuum annealing activated and nitrogen atmosphere annealing activated devices.

between high vacuum annealing activated and nitrogen atmosphere annealing activated devices.

Download figure:

Standard imageIn fig. 3(c), we focus on electron mobility's dependency on density for both high vacuum annealing activated and nitrogen atmosphere annealing activated devices. Taking batch 1 as an example, the device with high vacuum activation annealing has a higher mobility. The mobility at the same density is increased by a factor of two by replacing nitrogen atmosphere annealing with high vacuum activation annealing. The results in fig. 3(d) show that our improvement by high vacuum annealing is universal for both intrinsic substrates and boron-doped substrates. Additionally, samples of batch 3 have higher mobilities than those of batches 1 and 2 for both methods, which may possibly be attributed to strain releasing and diffusing of impurity atoms induced by high vacuum activation annealing. Overall, to achieve a higher peak mobility, high vacuum activation annealing is a promising solution and an FZ substrate is a better choice.

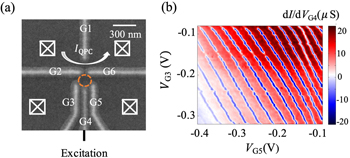

We demonstrate a single quantum dot using Cz wafers (batch 2) with an improved mobility of  by high vacuum activation annealing and the result shows that the commercial wafers after our processing can be used for fabricating quantum dot devices. The quantum dot design was based on a double top-gated architecture, similar to previous work conducted on GaAs and Si [51,52]. This single quantum dot and quantum point contact structure is confined by six gates between the Al2O3 layer and SiO2 layer. The structure of the planar gates is displayed in fig. 4(a). By detecting the charge sensing signal of the single dot, the standard stability diagram of the single dot can be obtained. In fig. 4(b), dozens of tunnelling lines are mapped by changing the gate voltages at G3 and G5. These parallel lines show a single dot behaviour. Moreover, the interval between two proximal lines gradually increases when lowering the gate voltages, corresponding to the change in the electron number in the dot. Clearly, these lines are not cut off by other lines arising from disorder. No impurities are involved in this regime. More than 15 consecutive Coulomb oscillations can be observed without visible parasitic dot effect. The collection of process described in the paper to improve the device mobility, in a long run, should help to improve the quality of Si MOS quantum dots.

by high vacuum activation annealing and the result shows that the commercial wafers after our processing can be used for fabricating quantum dot devices. The quantum dot design was based on a double top-gated architecture, similar to previous work conducted on GaAs and Si [51,52]. This single quantum dot and quantum point contact structure is confined by six gates between the Al2O3 layer and SiO2 layer. The structure of the planar gates is displayed in fig. 4(a). By detecting the charge sensing signal of the single dot, the standard stability diagram of the single dot can be obtained. In fig. 4(b), dozens of tunnelling lines are mapped by changing the gate voltages at G3 and G5. These parallel lines show a single dot behaviour. Moreover, the interval between two proximal lines gradually increases when lowering the gate voltages, corresponding to the change in the electron number in the dot. Clearly, these lines are not cut off by other lines arising from disorder. No impurities are involved in this regime. More than 15 consecutive Coulomb oscillations can be observed without visible parasitic dot effect. The collection of process described in the paper to improve the device mobility, in a long run, should help to improve the quality of Si MOS quantum dots.

Fig. 4: (a) Scanning electron microscopy image of a single quantum dot and quantum point contact (QPC) structure with buried oxide on a Si MOS heterostructure. G1–G6 are the depleted gates used to define the potential of the quantum well. Excitation is a sinusoidal waveform coming from a lock-in for charge sensing. (b) Charge stability diagram of the single quantum dot monitored via an adjacent quantum point contact. Each line corresponds to a tunnelling event of electrons.

Download figure:

Standard imageIn conclusion, we perform the quantum transport characterizations on silicon MOS Hall bars using commercial silicon wafers. We report that high vacuum activation annealing helps to increase the mobility of 2DEGs by a factor of two, leading to a peak mobility of  . We find that high vacuum activation annealing and selection of FZ wafers are helpful to approach the higher mobility and the behavior of our single dot device is a good example of improving the mobility for high-quality quantum dot formation. For further improvement in quantum devices, more efforts are still needed to handle residual impurities and defects at the interface between Si and SiO2. Our results may provide valuable insights into wafer optimization in silicon-based quantum computing.

. We find that high vacuum activation annealing and selection of FZ wafers are helpful to approach the higher mobility and the behavior of our single dot device is a good example of improving the mobility for high-quality quantum dot formation. For further improvement in quantum devices, more efforts are still needed to handle residual impurities and defects at the interface between Si and SiO2. Our results may provide valuable insights into wafer optimization in silicon-based quantum computing.

Acknowledgments

This work was supported by the National Key Research and Development Program of China (Grant No. 2016YFA0301700), the National Natural Science Foundation of China (Grant Nos. 61674132, 11674300 and 11625419), the Strategic Priority Research Program of the CAS (Grant No. XDB24030601), and the Anhui Initiative in Quantum Information Technologies (Grant No. AHY080000), and this work was partially carried out at the USTC Center for Micro and Nanoscale Research and Fabrication.