#### **PAPER • OPEN ACCESS**

# Fabrication of surface ion traps with integrated current carrying wires enabling high magnetic field gradients

To cite this article: Martin Siegele-Brown et al 2022 Quantum Sci. Technol. 7 034003

### Manuscript version: Accepted Manuscript

Accepted Manuscript is "the version of the article accepted for publication including all changes made as a result of the peer review process, and which may also include the addition to the article by IOP Publishing of a header, an article ID, a cover sheet and/or an 'Accepted Manuscript' watermark, but excluding any other editing, typesetting or other changes made by IOP Publishing and/or its licensors"

This Accepted Manuscript is© .

Original content from this work may be used under the terms of the <u>Creative Commons Attribution 4.0 licence</u>. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

View the article online for updates and enhancements.

## Fabrication of Surface Ion Traps with Integrated Current Carrying Wires enabling High Magnetic Field Gradients

Martin Siegele-Brown<sup>1†</sup>, Seokjun Hong<sup>1†</sup>, Foni Raphaël Lebrun-Gallagher<sup>1,2</sup>, Samuel James Hile<sup>1</sup>, Sebastian Weidt<sup>1,2</sup>, and Winfried Karl Hensinger<sup>1,2</sup>

<sup>1</sup>Sussex Centre for Quantum Technologies, University of Sussex,

Brighton, BN1 9RH, UK

<sup>2</sup>Universal Quantum Ltd, Brighton, BN1 6SB, UK

$^\dagger \text{These}$  authors contributed equally to this work.

E-mail: W.K.Hensinger@sussex.ac.uk

Keywords: microfabrication, surface ion traps, current carrying wires, magnetic field gradients, quantum computing

Abstract. A major challenge for quantum computers is the scalable simultaneous execution of quantum gates. One approach to address this in trapped ion quantum computers is the implementation of quantum gates based on static magnetic field gradients and global microwave fields. In this paper, we present the fabrication of surface ion traps with integrated copper current carrying wires embedded inside the substrate below the ion trap electrodes, capable of generating high magnetic field gradients. The copper layer's measured sheet resistance of  $1.12\,\mathrm{m}\Omega/\mathrm{sq}$  at room temperature is sufficiently low to incorporate complex designs, without excessive power dissipation at high currents causing a thermal runaway. At a temperature of 40 K the sheet resistance drops to  $20.9\,\mathrm{\mu}\Omega/\mathrm{sq}$  giving a lower limit for the residual resistance ratio of 100. Continuous currents of 13 A can be applied, resulting in a simulated magnetic field gradient of  $144\,\mathrm{T/m}$  at the ion position, which is  $125\,\mathrm{\mu m}$  from the trap surface for the particular anti-parallel wire pair in our design.

#### 1. Introduction

Since the first quantum gates using trapped ions were proposed by Cirac and Zoller [1], trapped ions have been considered to be a promising qubit platform to realise large-scale quantum information processing. Experiments have proven the capabilities of trapped ions to be used as physical qubits, including high-fidelity state preparation [2–4], universal gate operation [4–6] and readout [4,7], and long coherence times [4,8,9]. In addition to these experiments using single ion strings, there has also been research into expanding the ion trapping system into a large scale architecture, and increasing the number of qubits that can be processed in parallel and entangled for implementation

of more complex quantum algorithms [10, 11]. The key of this research, inspired by the proposals of Wineland et al. [12] and Kielpinski et al. [13], is making all macroscopic devices for trapping ions completely scalable. Surface ion traps developed using micro-electro-mechanical system (MEMS) fabrication technology [14–17] and the concept of junction nodes connecting linear ion trapping zones [18–20] have significantly increased the number of ions that can be trapped and controlled on a microchip. Optical and electrical components such as micro-mirrors [21] and optical waveguides [22–25], photodetectors [26–28], digital-to-analogue converters (DACs) [29], and trench capacitors [30] can be fabricated in microchips and integrated in the same chip together with ion traps.

A major challenge for increasing the number of qubits is the simultaneous large-scale control of quantum gates, and a few methods have been developed for trapped ions. For laser based gates, integrated optical waveguides and gratings [22–25] are a promising approach. As a different approach, laser free high fidelity gates have been demonstrated using oscillating magnetic field gradients [31,32]. Another approach is to use long-wavelength radiation combined with a static magnetic field gradient as proposed by Mintert and Wunderlich [33]. Weidt et al. have further built on this work and demonstrated a quantum computing approach where quantum gates can be executed simply by the application of a semi-static voltage to a microchip making use of locally applied magnetic field gradients, and global microwave and RF fields [34]. Lekitsch et al. have developed a microchip-based blueprint for a fault-tolerant quantum computer capable of hosting millions of qubits [35]. In the proposed architecture, microfabricated surface ion traps and integrated current-carrying wires (CCWs) are used to trap ions and generate a high static magnetic field gradient in designated gate zones on the chip.

Historically, CCWs have been used extensively for the confinement of neutral atoms, allowing the technology to shift from free-standing wires to more robust microfabricated atom chips [36]. In atom chips, a single layer of evaporated gold up to several micrometres thick is widely used for CCWs [37,38]. Furthermore, multilayer atom chips have been demonstrated [39], some allowing currents up to 10 A in 15 µm thick CCWs [40], including one featuring 2 µm thick copper CCWs embedded into the silicon [41]. For ion traps with integrated current carrying wires, the wires need to be combined with a top layer structure capable of applying the required high RF voltages, and dielectrics in sight of the ion should be avoided.

In ion traps with CCWs in the top layer, static axial magnetic field gradients of  $2.3-23\,\mathrm{T/m}$  have been demonstrated [42–44]. Oscillating magnetic field gradients of 7, 35 and  $55\,\mathrm{T/m}$  in the  $1-3.2\,\mathrm{GHz}$  range have been reported at ion heights of 75, 30 and  $35\,\mu\mathrm{m}$  respectively [45–47], as well as a radial gradient at 5 MHz of  $152(15)\,\mathrm{T/m}$  at an ion height of  $30\,\mu\mathrm{m}$  [32], all with the CCWs located in the top layer of the ion trap. In a different implementation where  $127\,\mu\mathrm{m}$  thick copper wires have been placed on a chip carrier below the ion trap, a static magnetic field gradient of  $16\,\mathrm{T/m}$  at an ion height of  $96.9\,\mu\mathrm{m}$  has been achieved [48].

In our design the CCWs are embedded in the silicon substrate perpendicular to the

#### Fabrication of Surface Ion Traps with Integrated Current Carrying Wires

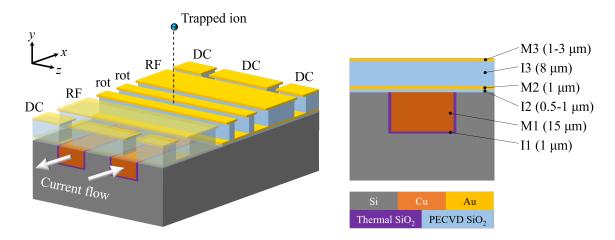

Figure 1: Schematic of the proposed surface ion trap with integrated CCWs (not to scale). A set of segmented DC electrodes and RF electrodes are shown as transparent to show part of the copper wires integrated under the electrodes. The vertical dimensions of the ion trap electrodes and CCWs are shown on the right.

RF trapping electrodes as shown in Figure 1. In this concept, the design of the CCWs is completely independent from the design of the top electrode layer. This removes the constraints that have limited the axial gradient with CCWs in the top layer, without moving the CCWs significantly further away from the ion. With a sufficiently low sheet resistance of the copper for the management of thermal dissipation from the current, high currents in excess of 10 A can be applied allowing magnetic field gradients in the range of 100–150 T/m at an ion position 125 µm from the trap surface.

In this paper, we present the design and fabrication of surface ion traps with integrated CCWs for high magnetic field gradients. A fabrication process consisting of integration of copper wires in the silicon substrate and fabrication of ion trap electrodes on top of this structure was developed. In order to reduce the effect of stray electric fields induced by built-up charges on dielectric surfaces, gold was used for conducting layers exposed to the ion to avoid native oxide formation, and the thick oxide layer underlying the uppermost metal layer was undercut. Application of high currents up to 13 A continuous, resulting in a simulated magnetic field gradient of  $144\,\mathrm{T/m}$  at the ion position of  $125\,\mathrm{\mu m}$ , was demonstrated on the fabricated wires, and power dissipation was measured. The fabricated chips were also used to trap  $^{171}\mathrm{Yb^+}$  ions. Considering the gate mechanism, a magnetic field gradient of  $100-150\,\mathrm{T/m}$  should enable much stronger sideband transitions and is predicted to give rise to a two-qubit gate fidelity of  $\sim 99.9\,\%$  [34], significantly higher than the fault-tolerant threshold for the surface code [49].

Fabrication of Surface Ion Traps with Integrated Current Carrying Wires

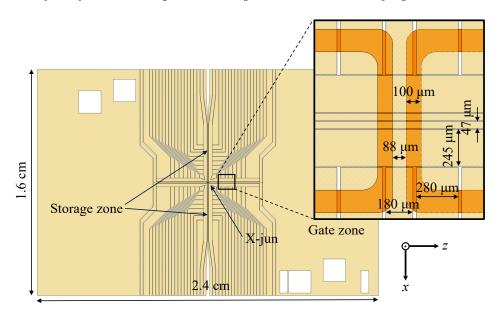

Figure 2: Layout design of ion trap showing the gate zone and storage zones. Ions can be shuttled between zones via the X-junction in the centre of the device. The white squares represent the bonding pads for the CCWs. The magnified view shows the electrode and CCW design in the gate zone.

#### 2. Design

The vertical dimensions of the designed ion trap electrodes are shown in Figure 1. The thickness of the oxide layer (I3) isolating the top layer (M3) and the ground plane (M2) is  $8 \, \mu m$ , where we measured a flashover voltage of over  $250 \, V_{amp}$  at  $15 \, MHz$  between the RF electrode and the ground plane using a test structure chip. The ion height numerically simulated by the lateral design of electrodes is  $125 \, \mu m$  from the electrode surface. The two central DC electrodes between the RF rails are used to apply compensating DC voltages for principal axis rotation.

The gate zone incorporating the CCWs is located in one of the four arms of the X-junction (Figure 2). The design of the X-junction is adapted from [50]. The trapped ions can be shuttled to two storage zones with a low magnetic field of  $< 2 \,\mathrm{mT}$  placed in the two perpendicular arms. Two parallel wires are placed perpendicular to the RF rails, and DC currents with opposite directions are applied to the wires to maximise the magnetic field gradient at the ion position.  $100 \,\mathrm{\mu m}$ ,  $15 \,\mathrm{\mu m}$ , and  $88 \,\mathrm{\mu m}$  for the width and depth of wires and the distance between the wires respectively were chosen to give a good trade-off between current density and power dissipation, and maximum magnetic field gradient. The gradient is only reduced by  $17 \,\%$  compared to the ideal case of two infinitely thin wires located on the silicon surface, while limiting the current density to  $1 \times 10^6 \,\mathrm{A/cm^2}$  at  $15 \,\mathrm{A}$ . The overall CCW structure corresponds to a wire with a length to width ratio of 390. Finite element method simulation results show that by applying  $13.4 \,\mathrm{A}$  to the wires, a magnetic field gradient of  $150 \,\mathrm{T/m}$  along the longitudinal trap

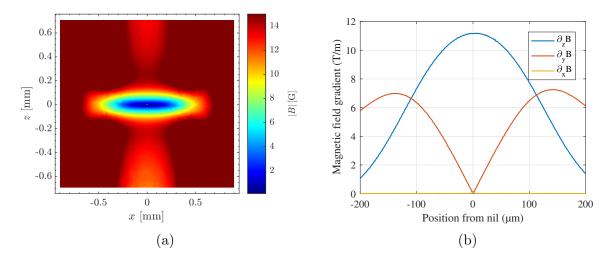

Figure 3: Finite element method simulation results of the CCW structure designed for this experiment per 1 A input current. (a) Magnetic field magnitude |B| in a horizontal plane at the trapping height  $(h_{ion} = 125 \,\mu\text{m})$  with the magnetic field quadrupole clearly visible in the centre at  $(x = 0; y = h_{ion}; z = 0)$ . (b) x-, y-, and z-components of the gradient of the magnetic field magnitude along the axial trapping axis z. Close to the quadrupole centre, the magnetic field gradient  $\partial B$  is maximal with a gradient of 11.1 T/m per 1 A input current. At 13.4 A this gives the 150 T/m necessary for high fidelity gates proposed by Weidt et al. [34].

axis can be generated at the ion position (Figure 3). Depending on the precise gate implementation, a gradient in the range of 100–150 T/m is desirable.

A further consideration for the CCW design is ohmic power loss and substrate heating, mainly determined by the resistance of the wires. The 15 µm thick copper layer has a sheet resistance of  $1.12\,\mathrm{m}\Omega/\mathrm{sq}$  at room temperature. This low sheet resistance allows for a resistance at room temperature of  $438\,\mathrm{m}\Omega$  for our CCWs in series, despite the complex design. The resistance is predicted to be reduced to  $15.0\text{--}49.5\,\mathrm{m}\Omega$  at the intended operating temperature of  $40\text{--}70\,\mathrm{K}$ , assuming a copper layer with a residual resistance ratio (RRR) of 50. This resistance corresponds to a power dissipation of  $2.3\,\mathrm{W}$  when applying  $10\,\mathrm{A}$  assuming a cooling system with a base temperature of  $40\,\mathrm{K}$  and  $5\,\mathrm{K/W}$  overall thermal resistance, which is a conservative estimate for our setup from previous measurements.

#### 3. Fabrication

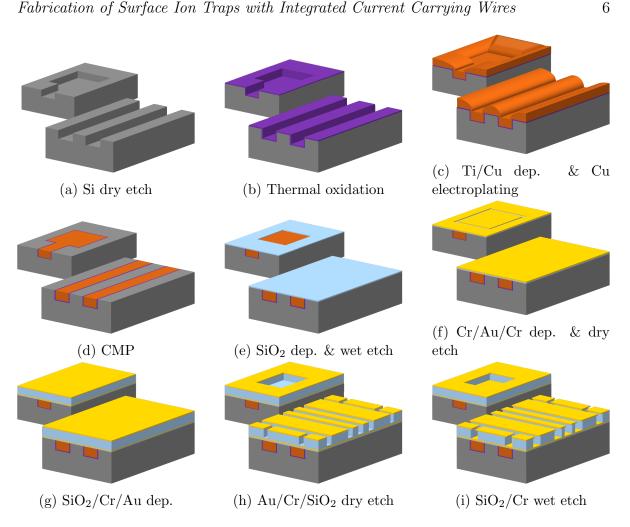

This section describes the fabrication process of integrating the CCWs into the silicon substrate and building ion trap electrodes on top of the CCW-integrated wafer. First, the CCW layout is photolithographically patterned on the silicon wafer using a conventional deep reactive ion etching (DRIE) process (Figure 4(a)). After stripping the used resist followed by a standard RCA clean, the wafers are thermally oxidised in a

Figure 4: Fabrication process flow. Note that the adhesion layers and photolithography steps are not shown in the schematics. Positive photoresist was used for all the lithography steps. The schematics at the front and back show the process flow of the gate zone area and bonding pads of the CCWs respectively. All schematics not to scale.

furnace tube to grow wet oxide of 1  $\mu$ m, forming an insulating layer between the silicon substrate and the CCW (Figure 4(b)). Then, Ti/Cu with a thickness of 10/200 nm is deposited by a sputtering process, and using this as an adhesion and seed layer, a 25  $\mu$ m thick copper layer is subsequently electroplated to form the CCWs (Figure 4(c)). The fabricated structures are planarised by a three-step sequence that consists of diamond milling and two chemical mechanical polishing (CMP) steps. Optimising the process parameters, a dishing of approximately 100 nm for 100  $\mu$ m to 1500  $\mu$ m wide patterns was achieved. This concludes the fabrication of the CCW base wafer (Figure 4(d)).

Fabrication of the ion trap electrodes starts with plasma-enhanced chemical vapour deposition (PECVD) of a 0.5–1 µm-thick SiO<sub>2</sub> layer (Figure 4(e)). The oxide layer is patterned by wet etching using buffered oxide etchant (BOE) (HF:NH<sub>4</sub>F = 1:7) to open the bonding pads for the CCWs. Then, a Cr/Au/Cr layer of 10/1000/10 nm is sputtered and ion-beam-etched (IBE) to provide the ground plane as well as the bonding pads for

the CCWs (Figure 4(f)). The thin chromium layer is used to increase adhesion between silicon oxide and gold. Next, an  $8\,\mu$ m-thick SiO<sub>2</sub> layer and  $10/1000-3000\,\mu$ m-thick Cr/Au layer are deposited (Figure 4(g)). These two layers are dry etched sequentially using the same photoresist mask (Figure 4(h)). The good uniformity (4(1)%) of the deep oxide etching process allows stopping 750(250) nm before reaching the Cr/Au/Cr layer, in order not to expose the gold to the oxide etching chemistry. The remaining oxide is etched by BOE based wet etching. This wet etching also etches the sidewalls of the oxide pillar, resulting in the formation of the electrode undercut structure (Figure 4(i)). After the BOE, the exposed Cr adhesive layer over the Au ground plane is removed by an additional wet etching process. Finally, a  $10/500\,\mu$ m Cr/Au layer is sputtered on the back of the wafer to improve indium bonding of the traps.

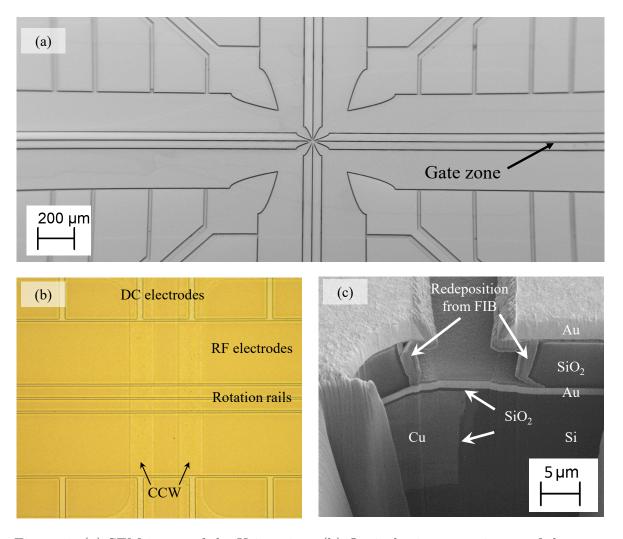

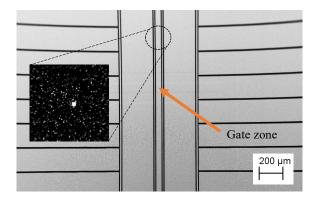

An optical microscope image showing the top view of the gate zone, a scanning electron image (SEM) image of the X-junction, and an SEM image of the cross-section

Figure 5: (a) SEM image of the X-junction. (b) Optical microscope image of the trap, showing the gate zone. (c) SEM image of the cross-section of the device made by a focused ion beam.

of the devices fabricated by a focused ion beam (FIB) are shown in Figure 5. The cross-section is placed at the end of the west arm of the X-junction where a routing wire of the CCW is parallel to the two rotation electrodes, which are separated by 5  $\mu$ m. The oxide below the rotation electrodes shows the desired undercut of 3(1)  $\mu$ m from the oxide wet etch. Every surface in the line of sight of the ion beam impact is covered with some redeposited material, which is unavoidable. The resistance between the copper tracks and surrounding conducting layers was higher than our measurement limit (10 M $\Omega$ ), and no unintended electrical short was observed between ion trap electrodes.

#### 4. Experiments

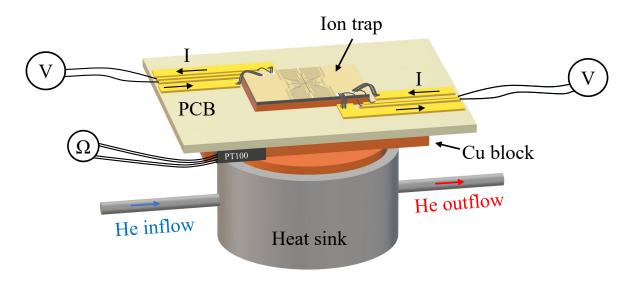

The resistance of the CCW at room temperature was measured using four-terminal sensing with  $100\,\mathrm{mA}$  source current. The fabricated CCWs match the expected resistance within <1%. To evaluate performance at low temperatures, the device was mounted in a custom cryogenic system as shown in Figure 6. The fabricated trap was indium soldered to a copper block, which extends through a hole in the printed circuit board (PCB) to which it is attached. The CCWs were connected by ten  $25\times125\,\mathrm{\mu m}$  ribbon bonds per pad to the PCB and by one ribbon bond for voltage sensing connections. The temperature was measured with a calibrated PT100 (Lakeshore Pt-111-14H) attached to the copper block. The copper block was then mounted on a heat sink (using AuSn preforms in-between) located in a custom ultra high vacuum

Figure 6: The fabricated trap is bonded to a copper block using indium with a PCB attached. The CCWs are connected by ten  $25 \times 125 \,\mu m$  aluminium ribbon bonds per pad to a printed circuit board (PCB) and by one ribbon bond for voltage sensing connections. The temperature is measured using a PT100 attached to the copper block. The copper block is then mounted on a heat sink located in a custom UHV test chamber, which is connected to a custom closed-loop cryogenic helium gas circulation system.

(UHV) test chamber, which was supplied by a custom closed loop cryostat [51]. The measurements were performed at a pressure of  $\sim 10^{-6}$  mbar and a base temperature of 38(2) K.

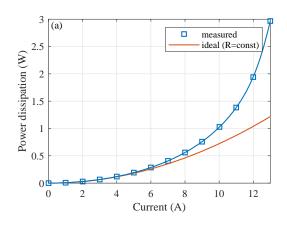

To characterise the power consumption of the CCWs, current was applied through all CCWs in series, and the voltage drop was directly measured at the CCW pads (via sensing bond wires). At a current of 10 A the power dissipation is 1028(10) mW (Figure 7(a)), which is 1.43 times higher than it would be without heating the trap. The rise in resistivity by a factor of 1.43 corresponds to a rise in temperature of the CCWs from 38 K to 43 K, while the temperature measured on the copper block is 40 K. The maximum continuous current of 13 A was limited by thermal runaway which can be improved by optimising the thermal anchoring.

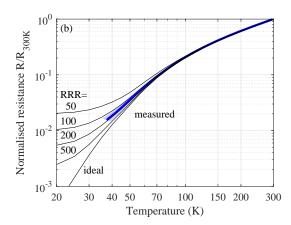

To obtain the temperature dependence of the resistance, the helium flow was turned off and the resistance was measured as the system was heating up  $(2 \,\mathrm{K/min})$ . A probe current of  $10 \,\mathrm{mA}$  was used for the four-terminal sensing of the CCW resistance. At  $40(1) \,\mathrm{K}$  the resistance drops from  $438(1) \,\mathrm{m}\Omega$  by a factor of 54(2) to  $8.2(4) \,\mathrm{m}\Omega$  and at  $70(1) \,\mathrm{K}$  by a factor of 10.7(1) to  $40.8(4) \,\mathrm{m}\Omega$ . This corresponds to a sheet resistance of  $20.9(9) \,\mathrm{\mu}\Omega/\mathrm{sq}$  at  $40(1) \,\mathrm{K}$  and  $104(1) \,\mathrm{\mu}\Omega/\mathrm{sq}$  at  $70(1) \,\mathrm{K}$ . Figure 7(b) shows the normalised resistance (blue with uncertainty as shaded area) compared to Cu with an RRR of 50, 100, 200 and 500 and pure Cu (data from [52]). The measurement setup does not allow a precise number for RRR to be obtained, but is estimated as  $180^{+215}_{-65}$  with a lower bound of 100.

Fabricated chips with integrated CCWs were successfully used to trap <sup>171</sup>Yb<sup>+</sup> ions as shown in Figure 8. We note that the chip used for trapping is slightly modified earlier

Figure 7: (a) Measured power dissipation over applied current through the whole CCW structure, compared to the ideal case where the trap does not heat up. (b) Normalised resistivity of CCW over temperature. The measured resistance (blue with the uncertainty as shaded area) is compared to copper with different RRR for comparison.

Fabrication of Surface Ion Traps with Integrated Current Carrying Wires

Figure 8: SEM image of the fabricated device. The inlay shows an image of a trapped ion captured by an electron-multiplying charge-coupled device (EMCCD) sensor.

version of the design described in Sec. 3 featuring an aluminium ground plane instead of a gold ground plane. We had adjusted the fabrication process in order to avoid an aluminium electrode, as such an electrode could potentially form a very thin oxide layer and charge up. We also replaced the central ground electrode and four thin rotation electrodes by two central DC electrodes for the newer design to enable a simpler principal axis rotation and to enable more undercut of the dielectric below the electrodes. During trapping, we note that we did not observe any adverse effects because of the aluminium ground plane. Ions have been trapped on this device, frequently for 7–16 h.

#### 5. Conclusion and outlook

We have presented the fabrication of surface ion traps with current carrying wires integrated into the silicon substrate. The dishing of the CCWs is well controlled, with  $100\,\mathrm{nm}$  for both small features and large features, ensuring the electrical performance is not compromised. The residual resistance ratio is estimated as  $180^{+215}_{-65}$  with a lower limit of 100 giving a resistance close to that of pure copper at the temperature ranges in our application. These devices are capable of providing high currents of  $13\,\mathrm{A}$  continuous for high static magnetic field gradients of  $144\,\mathrm{T/m}$ , at an ion position of  $125\,\mathrm{\mu m}$  from the trap surface. These results indicate that the devices are suitable for high fidelity quantum gates based on static magnetic field gradients and global microwave fields, constituting a promising approach for building practical trapped ion quantum computers with millions of qubits.

#### Acknowledgment

The authors would like to thank Knut Gottfried, Cyrille Hibert, Didier Bouvet and Joffrey Pernollet for helpful discussions about the fabrication process, Reuben Puddy and Zak Romaszko for work on the early designs, and Mariam Akhtar and Falk Bonus for performing the trapping runs. Work was carried out at a number of facilities

including the Center of MicroNanoTechnology (CMi) at École polytechnique fédérale de Lausanne (EPFL), the London Centre for Nanotechnology (LCN) and the Scottish Microelectronics Centre (SMC) at the University of Edinburgh.

This work was supported by the U.K. Engineering and Physical Sciences Research Council via the EPSRC Hub in Quantum Computing and Simulation (EP/T001062/1), the U.K. Quantum Technology hub for Networked Quantum Information Technologies (No. EP/M013243/1), the European Commission's Horizon-2020 Flagship on Quantum Technologies Project No. 820314 (MicroQC), the U.S. Army Research Office under Contract No. W911NF-14-2-0106 and Contract No. W911NF-21-1-0240, the Office of Naval Research under Agreement No. N62909-19-1-2116, the Luxembourg National Research Fund (FNR) (Project Code 11615035), and the University of Sussex.

#### References

- [1] Cirac J I and Zoller P 1995 Physical review letters 74 4091

- [2] Wunderlich C, Hannemann T, Körber T, Häffner H, Roos C, Hänsel W, Blatt R and Schmidt-Kaler F 2007 Journal of Modern Optics 54 1541–1549

- [3] Blatt R and Wineland D 2008 Nature  $\mathbf{453}$  1008

- [4] Harty T P, Allcock D T C, Ballance C J, Guidoni L, Janacek H A, Linke N M, Stacey D N and Lucas D M 2014 Physical review letters 113(22) 220501

- [5] Monroe C, Meekhof D M, King B E, Itano W M and Wineland D J 1995 *Physical review letters* **75** 4714

- [6] Akerman N, Navon N, Kotler S, Glickman Y and Ozeri R 2015 New Journal of Physics 17 113060

- [7] Noek R, Vrijsen G, Gaultney D, Mount E, Kim T, Maunz P and Kim J 2013 Opt. Lett. 38 4735–4738

- [8] Timoney N, Baumgart I, Johanning M, Varón A, Plenio M, Retzker A and Wunderlich C 2011 Nature 476 185

- [9] Wang P, Luan C Y, Qiao M, Um M, Zhang J, Wang Y, Yuan X, Gu M, Zhang J and Kim K 2021 Nature communications 12 1–8

- [10] Brown K R, Kim J and Monroe C 2016 npj Quantum Information 2 1–10

- [11] Bruzewicz C D, Chiaverini J, McConnell R and Sage J M 2019 Applied Physics Reviews 6 021314

- [12] Wineland D J, Monroe C, Itano W M, Leibfried D, King B E and Meekhof D M 1998 Journal of research of the National Institute of Standards and Technology 103 259

- [13] Kielpinski D, Monroe C and Wineland D J 2002 Nature 417 709

- [14] Stick D, Hensinger W, Olmschenk S, Madsen M, Schwab K and Monroe C 2006 Nature Physics 2 36–39

- [15] Seidelin S, Chiaverini J, Reichle R, Bollinger J J, Leibfried D, Britton J, Wesenberg J H, Blakestad R B, Epstein R J, Hume D B, Itano W M, Jost J D, Langer C, Ozeri R, Shiga N and Wineland D J 2006 *Physical review letters* **96**(25) 253003

- [16] Hughes M D, Lekitsch B, Broersma J A and Hensinger W K 2011 Contemporary Physics 52 505–529

- [17] Romaszko Z D, Hong S, Siegele M, Puddy R K, Lebrun-Gallagher F R, Weidt S and Hensinger W K 2020 Nature Reviews Physics 2 285–299

- [18] Hensinger W K, Olmschenk S, Stick D, Hucul D, Yeo M, Acton M, Deslauriers L, Monroe C and Rabchuk J 2006 Applied Physics Letters 88 034101

- [19] Amini J M, Uys H, Wesenberg J H, Seidelin S, Britton J, Bollinger J J, Leibfried D, Ospelkaus C, VanDevender A P and Wineland D J 2010 New journal of Physics 12 033031

- [20] Wright K, Amini J M, Faircloth D L, Volin C, Doret S C, Hayden H, Pai C, Landgren D W, Denison D, Killian T et al. 2013 New Journal of Physics 15 033004

- [21] Merrill J T, Volin C, Landgren D, Amini J M, Wright K, Doret S C, Pai C, Hayden H, Killian T, Faircloth D et al. 2011 New Journal of Physics 13 103005

- [22] Mehta K K, Bruzewicz C D, McConnell R, Ram R J, Sage J M and Chiaverini J 2016 Nature nanotechnology 11 1066–1070

- [23] Mehta K K, Zhang C, Malinowski M, Nguyen T L, Stadler M and Home J P 2020 Nature 586 533–537

- [24] Niffenegger R J, Stuart J, Sorace-Agaskar C, Kharas D, Bramhavar S, Bruzewicz C D, Loh W, Maxson R T, McConnell R, Reens D et al. 2020 Nature 586 538-542

- [25] Ivory M, Setzer W, Karl N, McGuinness H, DeRose C, Blain M, Stick D, Gehl M and Parazzoli L 2021 Physical Review X 11 041033

- [26] Eltony A M, Wang S X, Akselrod G M, Herskind P F and Chuang I L 2013 Applied Physics Letters 102 054106

- [27] Todaro S L, Verma V B, McCormick K C, Allcock D T C, Mirin R P, Wineland D J, Nam S W, Wilson A C, Leibfried D and Slichter D H 2021 Physical review letters 126(1) 010501

- [28] Setzer W, Ivory M, Slobodyan O, Van Der Wall J, Parazzoli L, Stick D, Gehl M, Blain M, Kay R and McGuinness H 2021 Applied Physics Letters 119 154002

- [29] Stuart J, Panock R, Bruzewicz C, Sedlacek J, McConnell R, Chuang I, Sage J and Chiaverini J 2019 Physical Review Applied 11 024010

- [30] Guise N D, Fallek S D, Stevens K E, Brown K, Volin C, Harter A W, Amini J M, Higashi R E, Lu S T, Chanhvongsak H M et al. 2015 Journal of Applied Physics 117 174901

- [31] Zarantonello G, Hahn H, Morgner J, Schulte M, Bautista-Salvador A, Werner R, Hammerer K and Ospelkaus C 2019 *Physical review letters* **123** 260503

- [32] Srinivas R, Burd S, Knaack H, Sutherland R, Kwiatkowski A, Glancy S, Knill E, Wineland D, Leibfried D, Wilson A C et al. 2021 Nature 597 209–213

- [33] Mintert F and Wunderlich C 2001 Physical review letters 87(25) 257904

- [34] Weidt S, Randall J, Webster S C, Lake K, Webb A E, Cohen I, Navickas T, Lekitsch B, Retzker A and Hensinger W K 2016 Physical review letters 117(22) 220501

- [35] Lekitsch B, Weidt S, Fowler A G, Mølmer K, Devitt S J, Wunderlich C and Hensinger W K 2017 Science Advances 3 e1601540

- [36] Folman R, Krüger P, Schmiedmayer J, Denschlag J and Henkel C 2002 Microscopic atom optics: From wires to an atom chip (*Advances In Atomic, Molecular, and Optical Physics* vol 48) ed Bederson B and Walther H (Academic Press) pp 263–356

- [37] Folman R, Krüger P, Cassettari D, Hessmo B, Maier T and Schmiedmayer J 2000 Physical Review Letters 84 4749

- [38] Groth S, Krüger P, Wildermuth S, Folman R, Fernholz T, Schmiedmayer J, Mahalu D and Bar-Joseph I 2004 Applied Physics Letters 85 2980–2982

- [39] Trinker M, Groth S, Haslinger S, Manz S, Betz T, Schneider S, Bar-Joseph I, Schumm T and Schmiedmayer J 2008 Applied Physics Letters 92 254102

- [40] Chuang H C, Weng C W and Li H F 2011 Journal of Micromechanics and Microengineering 21 125009

- [41] Chuang H C, Salim E A, Vuletic V, Anderson D Z and Bright V M 2011 Sensors and Actuators A: Physical 165 101–106

- [42] Wang S X, Labaziewicz J, Ge Y, Shewmon R and Chuang I L 2009 Applied Physics Letters **94** 094103

- [43] Welzel J, Bautista-Salvador A, Abarbanel C, Wineman-Fisher V, Wunderlich C, Folman R and Schmidt-Kaler F 2011 *The European Physical Journal D* **65** 285–297

- [44] Kunert P, Georgen D, Bogunia L, Baig M, Baggash M, Johanning M and Wunderlich C 2014 Applied Physics B 114 27–36

- [45] Harty T, Sepiol M, Allcock D, Ballance C, Tarlton J and Lucas D 2016 Physical Review Letters 117 140501

- [46] Warring U, Ospelkaus C, Colombe Y, Brown K R, Amini J, Carsjens M, Leibfried D and Wineland

D J 2013 Physical Review A 87 013437

- [47] Hahn H, Zarantonello G, Bautista-Salvador A, Wahnschaffe M, Kohnen M, Schoebel J, Schmidt P O and Ospelkaus C 2019 Applied Physics B 125 1–10

- [48] Welzel J, Stopp F and Schmidt-Kaler F 2018 Journal of Physics B: Atomic, Molecular and Optical Physics 52 025301

- [49] Fowler A G, Mariantoni M, Martinis J M and Cleland A N 2012 Physical Review A 86 032324

- [50] Mokhberi A, Schmied R and Willitsch S 2017 New Journal of Physics 19 043023

- [51] Lebrun-Gallagher F R, Johnson N, Akhtar M, Weidt S, Bretaud D, Hile S J, Owens A and Hensinger W K 2021 arXiv preprint arXiv:2106.07580

- [52] Matula R A 1979 Journal of Physical and Chemical Reference Data 8 1147–1298