#### **PAPER • OPEN ACCESS**

## Nanofabrication of arrays of silicon field emitters with vertical silicon nanowire current limiters and self-aligned gates

To cite this article: S A Guerrera and A I Akinwande 2016 Nanotechnology 27 295302

View the article online for updates and enhancements.

### You may also like

- Exchange and electric fields enhanced spin thermoelectric performance of germanene nano-ribbon

Jun Zheng, Feng Chi and Yong Guo

- Two-qubit correlations revisited: average mutual information, relevant (and useful) observables and an application to remote state preparation

Paolo Giorda and Michele Allegra

- Nanotube field electron emission: principles, development, and applications Yunhan Li, Yonghai Sun and J T W Yeow

Nanotechnology 27 (2016) 295302 (11pp)

doi:10.1088/0957-4484/27/29/295302

# Nanofabrication of arrays of silicon field emitters with vertical silicon nanowire current limiters and self-aligned gates

#### S A Guerrera and A I Akinwande

Department of Electrical Engineering and Computer Science and Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139, USA

E-mail: guerrera@alum.mit.edu

Received 16 September 2015, revised 2 December 2015 Accepted for publication 11 January 2016 Published 13 June 2016

#### **Abstract**

We developed a fabrication process for embedding a dense array ( $10^8 \, \mathrm{cm}^{-2}$ ) of high-aspect-ratio silicon nanowires (200 nm diameter and  $10 \, \mu \mathrm{m}$  tall) in a dielectric matrix and then structured/exposed the tips of the nanowires to form self-aligned gate field emitter arrays using chemical mechanical polishing (CMP). Using this structure, we demonstrated a high current density ( $100 \, \mathrm{A \, cm}^{-2}$ ), uniform, and long lifetime (>100 h) silicon field emitter array architecture in which the current emitted by each tip is regulated by the silicon nanowire current limiter connected in series with the tip. Using the current voltage characteristics and with the aid of numerical device models, we estimated the tip radius of our field emission arrays to be  $\approx$ 4.8 nm, as consistent with the tip radius measured using a scanning electron microscope (SEM).

Keywords: Si nanowires, current limiters, MEMS, NEMS, field emission, cold cathodes

(Some figures may appear in colour only in the online journal)

#### 1. Introduction

Dense arrays of silicon nanowires embedded in a dielectric matrix are exciting structures with a potentially broad range of applications that include electronics and optoelectronic devices. Due to silicon's high refractive index, silicon nanowires exhibit strong resonant field enhancement to incident light when the nanowire diameter is of the order of the wavelength of light that is used to excite the nanowires [1]. Arrays of silicon nanowires (high refractive index) embedded in a dielectric matrix (low refractive index) form a 2D photonic crystal with an electromagnetic band gap with applications that include non-linear photonic crystals [2], biological and chemical sensors [3], light emitter diodes [4] and electrically-driven microcavity lasers [5]. In addition to photonic applications, silicon nanowires are also an exciting material for

Original content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

electronic devices. Most of the literature on silicon nanowires for electronic applications has focused on vertical Metal Oxide Field Effect Transistors (MOSFETs) [6] and individual nanowires placed horizontally on a substrate [7]. A variety of unconventional field-effect transistors (FETs) ranging from tunnel FETs to impact ionization FETs have been demonstrated using vertical silicon nanowire structures. These FETs address fundamental problems about the electrostatics needed to turn on a transistor with extremely small dimensions. A prime example of this class of electronic devices is the gate all-around silicon nanowire FET [6]. Another class of devices that could benefit from a dense array of silicon nanowires is vertical silicon field emission arrays. Both bottom-up [8] and top-down silicon field emission arrays [9] have been explored, and in both of these cases the silicon nanowire arrays are not embedded in dielectric structures. Very little attention has been given to densely packed, highly ordered, top-down fabricated, single crystal vertical silicon nanowire devices that are embedded in a dielectric matrix.

This paper explores the electronic device applications of dense arrays of silicon nanowires that are embedded in

1

dielectric matrices. The high-aspect-ratio nanowires form non-linear conduction channels that act in parallel when a voltage is applied across the two ends of the nanowires. The operation of the silicon nanowire current limiters have been explored in more detail in [9, 10]. At low applied drain-to-source voltage,  $V_{\rm DS}$ , the current,  $I_D$ , depends on the applied voltage with a linear conductance as the proportionality constant, where

$$I_D = \frac{A_{\rm E} q \mu_N n V_{\rm DS}}{L} \tag{1}$$

and q is the electronic charge,  $\mu_N$  is the mobility of electrons,  $A_{\rm E}$  is the effective cross-sectional area, L is the nanowire length, n is the electron density and  $V_{\rm DS}$  is the applied drainto-source voltage.  $A_{\rm E}$  corresponds to the cross-sectional area that is not depleted by states/traps at the Si/SiO<sub>2</sub> interface. It is smaller than the physical cross-sectional area, A, and it depends on the doping density,  $N_{\rm D}$ , and the interface states/trap density,  $D_{\rm it}$ .  $A_{\rm E}$  varies between the source and drain depending on the applied voltage and it is narrowest at the drain end. At high voltages, the velocity of the electrons saturate and the drain region pinches off, resulting in a constant current and current source-like behavior. Barring other device mechanisms, such as impact ionization in the nanowire, the current through the nanowire at saturation is given by

$$I_D = A_P qnv_{\text{sat}} (1 + \lambda V_{\text{DS}}) \tag{2}$$

where  $v_{\rm sat}$  is the electron saturation velocity in silicon,  $A_{\rm P}$  is the effective cross-sectional area at pinch-off and  $\lambda$  is the channel length modulation parameter. The current source-like behavior makes the 2D array of silicon nanowires an excellent platform for improving the performance of the gated field emitter array as it addresses the four major challenges that have prevented their adoption as cold cathodes in systems applications.

The four major challenges are (1) the large capacitance between the gate and the emitter electrodes that has limited switching and high-frequency performance [11]; (2) the insulator breakdown due to the injection of charge from the silicon substrate into the dielectric spacer between the gate and the emitter substrate or the gate electrode pad and the substrate [12]; (3) the erosion of field emitter tips due to bombardment by back streaming ions emanating from the impact ionization of neutral gas molecules desorbed from the anode or the gate that may include the formation of a plasma and (4) the emitter tip melting due to Joule heating and thermal runaway or a cathodic arc [13, 14]. A dense array of high-aspect-ratio silicon nanowires embedded in a dielectric matrix with current source behavior would be an ideal platform for addressing these problems.

Temple *et al* reduced the capacitance between the gate and the substrate of field emitter arrays in order to increase the unity current gain cut-off frequency,  $f_T$  [11, 15]. They used silicon pillar structures with aspect ratios of  $\approx 3.1:1$  (pillar height: pillar diameter). The pillar diameter has an impact on the minimum gate aperture, which influences the field factor,  $\beta$ , and consequently the slope of the Fowler–Nordheim plot,

$b_{\rm FN}$ . To reduce the gate-to-emitter capacitance,  $C_{\rm GE}$ , the aspect ratio of the field emitter arrays need to be increased further. The silicon nanowire (diameter = 200 nm, column height 10  $\mu$ m) embedded in a dielectric matrix presented here increases the aspect ratio to 50:1 (and potentially 100:1) and thus dramatically reduces the  $C_{\rm GE}/{\rm emitter}$ . Holland et al reduced the charge injection into the oxide between the gate and the emitter by increasing the insulator thickness to 4  $\mu$ m while keeping the gate aperture at a diameter of 1  $\mu$ m. Using this structure they reported a reduction in the electrostatic field across the insulator between the gate electrode and the substrate, leading to a dramatic decrease in the charge injection and an improvement of device reliability [16, 17]. Furthermore, the increase in the insulator thickness while keeping the gate aperture the same made the structure more amendable to field ionization at relatively low voltage, a physical process that requires more intense electrostatic fields [16–18]. In this work, the aspect ratio is increased to >50:1 while the gate aperture is reduced to 350 nm and the oxide thickness increased to  $10 \, \mu \text{m}$ , dramatically reducing the electrostatic field across the gate insulator thereby reducing time dependent dielectric breakdown (TDDB) and hence increasing lifetime [19, 20].

Takemura *et al* reported that a vertical current limiter connected in series to a small array of field emitters could improve reliability while not having any significant impact on the voltage drop across the field emitter and hence the field emission current. They showed that the vertical current limiter improved the lifetime of cathodes in traveling wave tubes [21]. Browning *et al* had earlier shown that cathodic arcs could be arrested or quenched if a high-valued resistor is placed in series with the emitter or gate of the field emitter with the central idea of limiting the current in the gate/emitter circuit [13, 22].

Velasquez-Garcia et al improved emission current uniformity [10, 23] by incorporating high-aspect-ratio silicon vertical current limiters [i.e. tip-to-tip spacing 10  $\mu$ m, column diameter 1  $\mu$ m, column height 100  $\mu$ m] in series with each emitter tip. The inclusion of a silicon vertical current limiter with current source behavior in series with each emitter tip improved uniformity, dramatically reduced the under-utilization of tips in large arrays, and also improved lifetime/ reliability. While Velasquez-Garcia et al were successful in improving emission current uniformity and reliability, their device required high operating gate-to-emitter voltage and only  $\approx 1\%$  of the emitted electrons were collected by the anode. This is because they needed to use an external gate electrode that is not self-aligned to the emitter, leading to the significant interception of the emitted electrons. More importantly, the high gate-to-emitter distance leads to a low field factor,  $\beta$ , electric field screening from neighboring silicon pillars, and hence high operating voltages. They could not fabricate proximate self-aligned gates because they could not embed their high-aspect-ratio silicon columns that form the basis for the current limiter in a dielectric matrix.

The technology enabled by embedding high-aspect-ratio silicon nanowires in a dielectric matrix reported in this paper increases the tip density by a factor of a 100 times compared

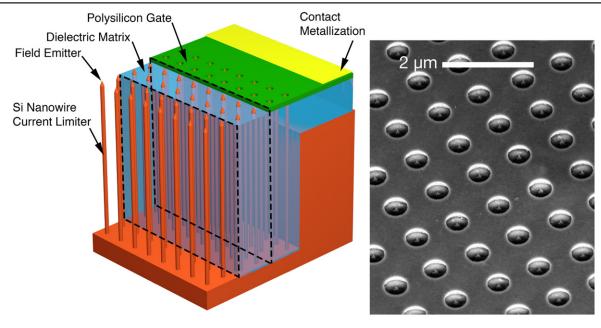

**Figure 1.** (Left) 3D rendering of device structure. For clarity, layers have been omitted in different regions of the rendering to show detail. In the front, the bare silicon nanowires [200 nm *diameter and* 10  $\mu$ m *height*] with sharp tips are shown. In the middle, the nanowires are shown embedded in a dielectric matrix. The complete device structure is shown in the back with annular polysilicon gate apertures [350 nm *diameter*]. (Right) SEM image of the completed device at 45° tilt.

to the device reported by Velasquez-Garcia et al, but it also reduces the operating voltage by a factor of 10 times, allowing the attainment of a very high current per tip (>1  $\mu$ A) and a current density of >100 A cm<sup>-2</sup> at low operating gateto-emitter voltages ( $V_{\text{GE}} < 75 \, \text{V}$ ) while also attaining long lifetimes ( $>100 \,\mathrm{h}$  @  $100 \,\mathrm{A} \,\mathrm{cm}^{-2}$ ). The presence of a current limiter in the emitter circuit improves both the emission current uniformity, lifetime and reliability. Current uniformity is improved because the electrons emitted from sharper tips which turn on at lower voltages (due to a higher field factor,  $\beta$ ) are regulated by the current limiter, while the duller tips that turn on at higher voltages emit lower currents. Reliability is improved because no tip ever attains a current level that is sufficient to lead to thermal runaway and melting because of the silicon nanowire current limiters. The current limiters also help to prevent cathodic arcs or plasma formation. Lifetime is improved because the electrostatic field across the insulator is significantly reduced leading to a reduction in TDDB [19, 20]. The final piece of the puzzle is the tip erosion from back-ion bombardment or arc formation due to the desorption of gas molecules from the anode. For our device characterization, we used a hollow anode structure that prevents the desorption of gas molecules from the anode upon impact by energetic electrons and the subsequent ionization of the desorbed molecules [24]. The positive ions erode the tip, which is often biased at the lowest potential. The current limiters based on silicon nanowires connected in series with the tips also prevent plasma formation and thus increase lifetime. Careful systems design and novel vacuum tube geometries can prevent back-ion bombardment in applications.

None of the previous work of integrating silicon pillars into field emitter arrays has been able to simultaneously achieve a high current, high current density, and a low voltage

while maintaining a long lifetime; this is due to the lack of a fabrication process that could simultaneously build dense, high-aspect-ratio silicon nanowires with sharp emitter tips and integrated, self-aligned extraction gates. In this paper, we report on a process for fabricating dense arrays of silicon nanowires that are embedded in a dielectric matrix and integrated with arrays of self-aligned gate field emitters. The array of field emitters with tip radii less than 5 nm are integrated with dense (1  $\mu$ m pitch) high-aspect-ratio silicon nanowires ( $\sim$ 200 nm diameter, 10  $\mu$ m tall). These devices have demonstrated a current >10 mA, a current density  $>100 \,\mathrm{A\,cm^{-2}}$  and an operating voltage,  $V_{\mathrm{GE,OP}} < 60 \,\mathrm{V}$ . Figure 1 is a rendering of a cross-section of the device and a scanning electron microscope (SEM) image of the completed structure. We also report on a new approach for determining the tip radii distribution in field emitter arrays that is based on current voltage characterization.

#### 2. Experimental details

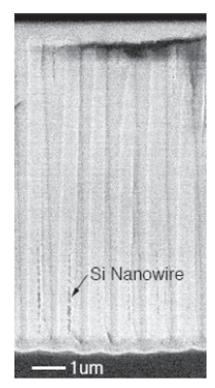

The field emitter arrays were fabricated on 150 mm n-type  $\langle 100 \rangle$  single crystal silicon wafers. Array sizes ranged from a single emitter to  $1000 \times 1000$  emitters. Each array has 1  $\mu \rm m$  emitter-to-emitter spacing. The emitters have tip radius <10 nm and are on top of a silicon nanowire that is <200 nm in diameter and 10 microns tall. A doped polysilicon gate electrode with 350 nm diameter surrounds the emitter to apply the electric field to the field emitter tip.

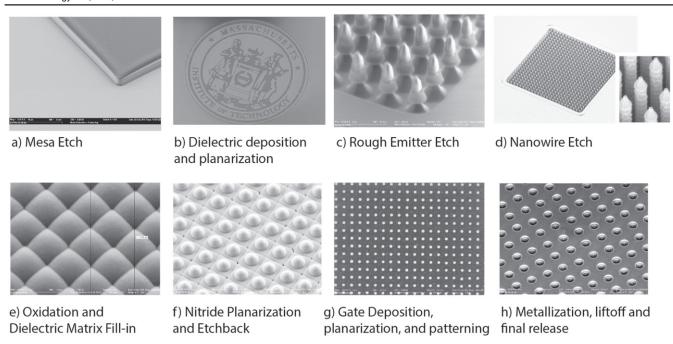

First, a mesa region on which the array of silicon nanowires capped with field emitter tips will later be fabricated is defined (figure 2(a)) by etching trenches around the array region. The trench is at least 200  $\mu$ m-wide and 2  $\mu$ m-deep.

Figure 2. Key steps in the fabrication of silicon field emitter arrays (FEAs) with vertical nanowire current limiters.

$5 \, \mu \text{m}$  of plasma-enhanced chemical vapor deposited (PECVD) oxide is deposited on both the front and the back of the wafer to fill in the trenches that were formed with the dielectric. In order to manage stress and prevent bowing, the deposition was carried out in two steps, with an anneal step in-between. Between depositions and after the second deposition, the wafers were annealed at 900 °C in N<sub>2</sub> ambient. Chemical mechanical polishing (CMP) is then used to planarize the surface and expose the bare silicon in the mesa region (figure 2(b)). A corresponding amount of the oxide film on the backside of the wafer was removed to balance the stress in the oxide films and remove the wafer bow that resulted after CMP. After planarization, approximately  $2 \mu m$ of SiO<sub>2</sub> remains in the trenches around the active regions. This SiO<sub>2</sub> isolates the gate electrode pad from the substrate and prevents dielectric breakdown of the oxide during normal device operation.

Next, 50 nm of dry thermal oxide is grown followed by the deposition of 250 nm of SiO<sub>2</sub> by PECVD. The oxide layers are an etch mask for patterning the emitters. The process to fabricate the nanoscale-sharp silicon tip and the silicon nanowire current limiter begins with an i-line stepper photolithography using a positive photoresist (Shipley SPR-700) to form 1  $\mu$ m pitch arrays of 0.5  $\mu$ m photoresist dots. It is critical that the array patterns are well-aligned (misalignment <50 nm) to the mesa regions. The oxide hard mask is patterned by CF<sub>4</sub>/CHF<sub>3</sub>/Ar reactive ion etching. After this etch, the tip has a diameter of about 200 nm. An SF<sub>6</sub> plasma is used to etch the silicon isotropically. The result of this etch, shown in figure 2(c), forms what will become the field emitter tips. Next, deep reactive ion etching (DRIE) is used to form the high-aspect-ratio silicon pillars. The pillars after the DRIE step with the SiO<sub>2</sub> hard mask removed is shown in figure 2(d). At this point, the pillars have a diameter of 400 nm, and are 10 microns tall. The diameter is somewhat less than the diameter of the hard mask used due to the undercutting of the oxide during the DRIE step because the etch is not perfectly anisotropic.

The remaining photoresist and the hard mask are stripped in an  $O_2$  plasma and 7:1 buffered hydrofluoric acid (BHF), respectively. To reduce the dimensions of both the pillar and the tip to their final dimensions, the wafers underwent wet oxidation at 950 °C. 950 °C is the temperature above which the viscoelastic flow of silicon dioxide occurs, which would deform the shape of the silicon dioxide and potentially result in blunt silicon tips [25–28]. A 2D finite element semiconductor process simulator (Silvaco ATHENA) was used to design the etching and oxidation steps to ensure that the emitter tip would be nanoscale-sharp and that the silicon nanowire would be <200 nm in diameter after this oxidation [9, 29]. The silicon nanowire has a diameter of  $\approx$ 200 nm and the column height is  $\approx$ 8–10  $\mu$ m. The silicon tip is formed by oxidation sharpening resulting in a tip radius of  $\approx$ 4–8 nm [9].

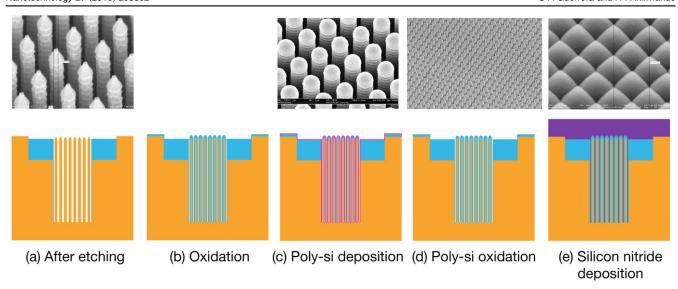

After the formation of the tip, the space between the silicon nanowires/tips is filled-in with a dielectric stack through a multi-step process shown in figure 3. This stack consists of silicon dioxide and silicon nitride formed through a combination of the deposition of undoped polysilicon films and the oxidation of the polysilicon films, and silicon nitride deposition. The undoped polysilicon is deposited at 625 °C using low-pressure chemical vapor deposition (LPCVD). At this temperature, the polysilicon has columnar growth and large grains [30]. In addition, due to the elevated temperature at which the deposition takes place, the deposition is reaction rate-limited [30] and the polysilicon has high surface mobility [31], allowing for conformal deposition into the deep voids between nanowires. The thickness of the deposited film is controlled so that after subsequent oxidation, a gap of

Figure 3. Process for filling in the voids between adjacent silicon nanowires with a dielectric matrix.

<50 nm remains between adjacent nanowires, and thus prevents the oxidizing surfaces from meeting. If the oxidation fronts do meet, they form keyhole voids or leave unoxidized polysilicon.

The remaining void is filled by 1  $\mu$ m of low-stress, silicon-rich silicon nitride (SiN<sub>x</sub>) deposited in a vertical tube reactor via LPCVD at 800 °C. The deposition reaction to form SiN<sub>x</sub> is also rate-limited and has high surface diffusion so that the nitride fills in the remaining gaps between pillars as shown in figure 2(e). A subsequent cross-section shows that this process creates a reproducible, consistently void-free dielectric matrix that completely surrounds the nanowires.

After the deposition of the dielectric stack, a self-aligned polysilicon gate is defined. A timed etch of the nitride is performed using CMP to bring the surface of the nitride to within approximately 100 nm of the top of the oxide domes. A cross-section of the void-free fill after planarization is shown in figure 4. The oxide domes will assist in the formation of the gate apertures. The oxide domes are exposed as shown in figure 2(f) through a timed wet etch using phosphoric acid at 160 °C (etch rate ~40 Å min<sup>-1</sup>). Phosphoric acid etches silicon nitride with a selectivity of ~20:1 relative to silicon dioxide. 800 nm of polysilicon gate electrode material that is in situ doped with phosphorus is next deposited. The dopants are activated using rapid thermal annealing at 950 °C for 30 s. A third CMP step planarizes the gate, and is timed to stop within 50 nm of the emitter tip. The grown and deposited oxide around the emitter tip defines the gate aperture, and the depth of the silicon nitride wet etch determines the gate thickness. Figure 2(g) shows the gate apertures after CMP.

After gate apertures are formed, the polysilicon gate is patterned through photolithography and a dry etch process. Ni/Ti/Au contact metal is deposited and patterned using a lift-off technique. The metal stack is sintered at 400 °C under forming gas for 30 min. During the sintering process, the nickel reacts with the polysilicon to form a nickel silicide, ensuring low contact resistance. Finally, a commercial pad

**Figure 4.** Void-free dielectric matrix with vertical silicon nanowires embedded in them after CMP planarization.

etchant (Silox Vapox III, Transene Co., Danvers, MA) removes the oxide encasing the tips to expose the tips. The sample is immediately dried with  $N_2$  and loaded into an ultrahigh vacuum for current-voltage (I-V) characterization. A tilted SEM image of the completed and released device is shown in figure 2(h).

During I-V characterization, an ion pump maintained the test chamber under an ultra-high vacuum, and the pressure was continually measured through the ion pump current. In addition a Bayard-Alpert gauge monitored outgassing. The pressure measured was below  $2 \times 10^{-10} \, \mathrm{Torr}$  during the

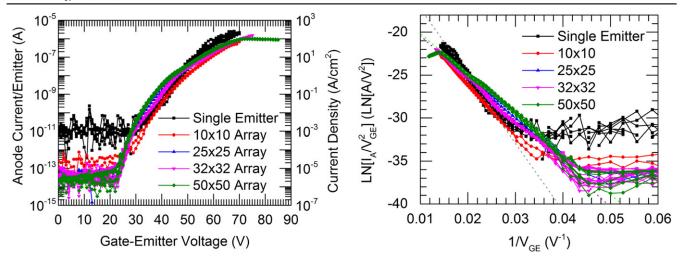

**Figure 5.** *I–V* characteristics (left) and Fowler-Nordheim plot (right) of several different field emission arrays, showing good agreement between different array sizes.

**Table 1.** Summary of device performance for the characteristics shown in figure 5.

| Array size     | Turn-on voltage (V) | Maximum voltage (V) | Maximum current      | Maximum current/tip  | FN<br>slope | FN intercept | FN intercept/tip |

|----------------|---------------------|---------------------|----------------------|----------------------|-------------|--------------|------------------|

| Single emitter | 31                  | 60                  | $2.5~\mu\mathrm{A}$  | $2.5~\mu\mathrm{A}$  | 785         | -9.39        | -9.39            |

| $10 \times 10$ | 27                  | 70                  | $67.8~\mu\mathrm{A}$ | 678 nA               | 610         | -9.33        | -13.9            |

| $25 \times 25$ | 22                  | 60                  | $11 \mu\text{A}$     | 176 nA               | 445         | -9.87        | -16.31           |

| $32 \times 32$ | 23                  | 65                  | 1.6 mA               | $1.55 \mu A$         | 498         | -8.49        | -15.42           |

| $50 \times 50$ | 22                  | 80                  | 2.6 mA               | $1.04 \mu\mathrm{A}$ | 468         | -7.72        | -15.54           |

course of the experiments. The electrons emitted by the field emitter array were collected by a stainless steel, bakeable, Faraday cup anode placed approximately 1 cm above the surface of the chip. Three Keithley 237 high voltage source measure units (SMUs) source voltage and measure the emitter, gate and anode currents. These SMUs have a  $\pm 1100\,\mathrm{V}$  range, can source current up to 10 mA, and measure current with a resolution  $<\!10\,\mathrm{pA}$ . MHV-5 electrical feedthroughs are used for electrical connection to the sample under test. Contact to the cathode was made to the backside through the chuck, and the gate was contacted with a tungsten probe.

#### 3. Results and discussion

Figure 5 shows the transfer characteristics for several devices with different array sizes. Multiple sweeps were taken to ensure that the characteristics were stable. From the I-V characteristics, we see that the arrays do show good agreement with each other when scaled by the number of tips in the array. Figure 5 also shows the Fowler–Nordheim (F–N) plot, wherein  $\ln(I_A/V_{\rm GE}^2)$  is plotted against the inverse of the gate-emitter voltage. We define the Fowler–Nordheim coefficients in the following way [32]:

$$\ln\left(\frac{I_A}{V_{GF}^2}\right) = \ln\left(a_{FN}\right) - \frac{b_{FN}}{V_{GF}} \tag{3}$$

where:

$$b_{\rm FN} = \frac{0.95 \cdot 6.87 \times 10^7 \cdot \phi^{3/2}}{\beta} \tag{4}$$

and

$$a_{\text{FN}} = \frac{\alpha \cdot 1.54 \times 10^{-6} \cdot \beta^2}{1.1\phi} \exp \times \left[ \frac{6.87 \times 10^7 \cdot 1.44 \times 10^{-7}}{\phi^{1/2}} \right]$$

(5)

where  $\phi$  is the barrier height (eV) and  $\beta$  is the field factor (cm<sup>-1</sup>) that converts the applied gate-emitter voltage to an effective tip surface field.

The Fowler–Nordheim plot is linear when the transfer characteristics are due to electron tunneling through the surface barrier. Small deviations from a linear relationship could be due to quantum effects in the emitter tip [33], a nontriangular tunneling barrier due to emitter geometry, or space charge limitation following Child's law [34].

The saturation of the anode current observed in the  $50 \times 50$  array above a gate-to-emitter voltage of  $70 \, V$  is not due to current limitation by the silicon nanowire, or any of these previously-stated effects. We observed that the saturation of the anode current is accompanied by a corresponding increase of the gate current. Thus, the saturation is likely due to the diversion of electrons to the gate after leaving the

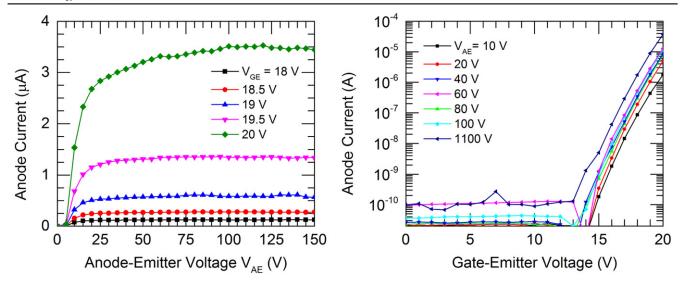

Figure 6. Output characteristics (left) and transfer characteristics (right) for a  $500 \times 500$  array.

emitter tip due to an insufficient anode field. This phenomenon could be mitigated by increasing the voltage on the anode or by bringing the anode physically closer to the surface of the emitter.

The devices reported were designed to achieve high current and hence they do not demonstrate clear evidence of current limitation during normal DC operation. They do demonstrate, however, that they are robust and uniform, and show the current scale with the number of tips in the array—thus implying that the silicon nanowires prevent catastrophic breakdown and improve uniformity.

Figure 6 shows the output characteristics and the transfer characteristic for a  $500 \times 500$  array (250 000 emitter tips). The device turns on at a gate-emitter voltage of approximately  $V_{\rm GE,ON} = 14 \, \rm V$ , and reaches  $> 3 \, \mu \rm A$  of current (>16 pA/ emitter) at  $V_{\rm GE} < 20$  V. As expected, for gate voltages  $>V_{\rm GE}$ , ON the anode voltage has very little dependence on the anode voltage. This low turn-on voltage can be attributed to the lognormal statistical variation of the tip radius of emitter tips [9], that arises from the fabrication process we employed to make the nanometer-sharp silicon emitters. Because of the distribution of the tip radius, at low voltages, the several very sharp (radius ~1 nm) emitters dominate the current characteristics. After prolonged emission or emission at higher voltages, the turn-on voltage shifts to higher voltages, perhaps due to the blunting of the emitter tips or the charging of the insulating oxide. At  $V_{\rm GE}=20\,{\rm V}$ , the gate transconductance reaches about  $30 \,\mu\text{S}$  (0.12 nS/tip). The transconductance shown is limited by the extremely low operating voltage of this cathode. An extension to higher voltages and currents, such as those reported by Whaley et al [35] would yield similar results, as the transconductance for a cathode scales exponentially with the gate voltage, and the currents for which they report transconductance were for  $V_{\rm GE} > 60 \, \rm V.$

#### 3.1. Electrical estimation of nanoscale emitter tip diameter

It is a significant challenge to image the fine structure of the tip with a transmission electron microscope (TEM) and scanning electron microscopy (SEM) due to the many different material layers in the field emitter structure, and the high packing density. The particular challenge of imaging the field emitter tip with high resolution SEM is the charging of the surrounding oxide layers. With TEM, there is a significant risk of damaging the tip geometry and re-depositing material onto the tip during sample preparation with focused ion beam milling. In the absence of traditional tools of analyzing the uniformity of our field emitter tips, we explore below the extraction of the tip distribution using our current voltage characteristics.

A simple analytical model relating the field factor,  $\beta$ , to the emitter tip radius is the ball-in-sphere model [36]. In this model, the emitter tip is modeled as a hard, metal sphere of radius r in a large, spherical shell of radius R. The relationship of the voltage applied between the spherical shell and the hard sphere to the electric field at the surface of the sphere is given by the solution of Laplace's equation in spherical coordinates.

$$\beta = \frac{1}{r} - \frac{1}{R - r} \approx \frac{1}{r} | r \ll R \tag{6}$$

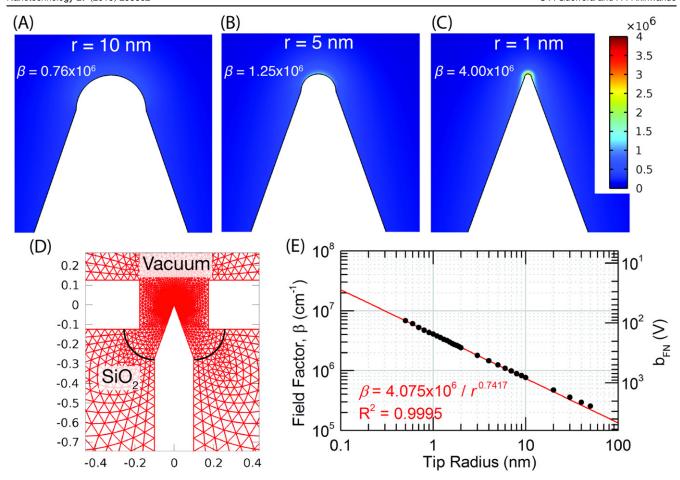

While this model is very simple to use and could give results that are reasonable to within an order of magnitude, it is not very accurate for realistic tip and gate geometries and it underestimates the tip radius for emitters that are sharper than 20 nm. To build a better estimate for the tip radius for our structure, we developed a finite element model for the silicon nanowires capped with field emitter tips embedded in a dielectric matrix using COMSOL Multiphysics. The element (silicon nanowire capped with silicon tip) is modeled using cylindrical symmetry around the central axis of the emitter (i.e. r = 0). The emitter is simulated as having an emitter

Figure 7. Finite element electrostatics simulation to determine the relationship between tip radius (r) and field factor  $(\beta)$  for the silicon nanowire with self-aligned gated tip. The nanowire is 200 nm in diameter and 10 microns tall, with a tip half-cone angle of 30 degrees. (A)–(C) Detail of the electric field around the apex of the tip for tip radii of 10 nm (A), 5 nm (B), and 1 nm (C). (D) Device structure materials and mesh for the electrostatic simulation showing different regions. (E) Fit of field factors with the model  $\beta = k/r^n$  shows good experimental agreement for this structure for r = 0.5–50 nm.

half-cone angle of 30°. The nanowire diameter is 200 nm, and the nanowire is 8 microns tall. The emitter tip radius is varied between 0.5 nm and 50 nm. The gate aperture is 350 nm, and the gate thickness is 250 nm. Aside from the tip, the pillar is buried in silicon dioxide with relative dielectric constant  $\varepsilon_{ox} = 3.9$ . The surface is assumed to be ideal with no fixed charge or surface states. In addition, it is assumed that there is no current or space charge in the system. The emitter is assumed to be a perfect conductor, that is, the voltage along the emitter surface is set to 0 V. The polysilicon gate is also modeled as a perfect conductor, and the voltage on the gate is 1 V. The boundary condition at r = 0 is set to  $\frac{\partial Er}{\partial r} = 0$ , and the solution of the potential and the electric field in the structure is reduced to a boundary value problem. With these boundary conditions (i.e.  $V_{\rm GE}=1~{\rm V}$ ), the maximum electric field at the apex of the field emitter in V cm<sup>-1</sup> is the field factor,  $\beta$ .

The finite element simulation of the tip geometry, shown in figures 7(A)–(C), plots the electric field proximal to tips of various emitter radii. By reducing the emitter tip from 10 nm to 1 nm, the field factor increased from  $0.76 \times 10^6 \, \mathrm{cm}^{-1}$  to  $4.0 \times 10^6 \, \mathrm{cm}^{-1}$ . If we plot the results for emitters in the range  $0.5 \, \mathrm{nm} < r < 50 \, \mathrm{nm}$ , we find the result shown in

figure 7(E). Dvorson *et al* [37], Jensen *et al* [38] and Ding *et al* [36] developed analytical models that show that the field factor for conical emitters follows the form  $\beta = k/r^n$ . By fitting an equation of that form to the field factors extracted from the numerical model, we obtained a very good fit to our data with  $\beta = 4.075 \times 10^6/r^{0.7417}$  cm<sup>-1</sup> for r in nm.

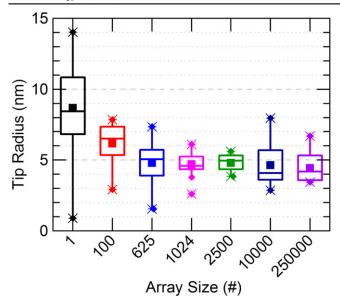

From the relationship between the tip radius and the field factor for our structure, we can use the slope of the Fowler–Nordheim plots of our *I–V* characteristics to estimate the average radius of the emitter tips in the array assuming that the silicon workfunction is its electron affinity. Over 150 *I–V* sweeps from 20 different devices were analyzed for their Fowler–Nordheim slopes, and their tip radii were extracted. The range of these *I–V* sweeps were varied, so as to access different parts of the array; i.e. at low extractor gate voltages, only the very sharp emitters are participating in emission. The results for the tip radii estimates for the different plots are summarized in the box chart shown in figure 8.

The mean of the average tip radii extracted from the current voltage characteristics of the field emitter arrays decreases from 8.7 nm for the single emitter to 4.8 nm for the  $25 \times 25$  array. It is likely that in the smaller arrays, edge

**Figure 8.** Box chart of the distribution of the average effective tip radii extracted from I-V characteristics and fitted to the tip radius using the extrapolation from the finite element model. The square in the center of each box indicates the mean value of the tip radius of the distribution. The horizontal line inside each box is the median value of the tip radius. The upper and lower bounds of the box show the first (Q1) and third quartiles (Q3) of the tip radius distribution; the height of the box is the inter-quartile range (IQR). The terminal points of the vertical lines extending from the boxes show approximately  $\pm 3\sigma$  (i.e.  $Q1 - 1.5 \times IQR$  and  $Q3 + 1.5 \times IQR$ ). The starred points are outliers.

effects have a large impact on the tip radius distribution. For example, in the  $10 \times 10$  array, 36% of emitters are on the perimeter, and 64% of emitters are either on the perimeter, or are nearest neighbors to the perimeter. As the size of the array increases, the percentage of emitters along the perimeter decreases. It is expected that the lithographic conditions (photon flux distribution) is not symmetric for nanowires/emitters situated on the perimeter. This will result in features that are slightly smaller. During oxidation, these slightly smaller features might have been over-oxidized, resulting in an emitter tip that is not as sharp [26]. This effect will be reduced by adding perimeter corrections to the mask.

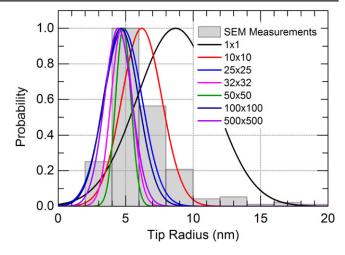

For arrays larger than 625, the average tip radius tends to be between 4 and 5 nm, consistent with previous work on silicon field emitter arrays. For arrays larger than 1000 emitters, the variation tends to be smaller. This is probably due to the law of large numbers, and the averaging effect that takes place with the large number of emitters. It was expected that there would be a slight trend for the tip radius to decrease with the array size due to the presence of a few sharper 'hero' emitters dominating the emission at lower voltages; however, this effect does not appear to be present in the data presented. Either the arrays are extremely uniform so that there are not many of these very sharp emitters, or the presence of the silicon pillar nanowire prevents them from contributing an overly large percentage of the current. If the statistics obtained from the *I–V* characterization are plotted as Gaussian

**Figure 9.** Probability density functions of the average effective tip radii of different array sizes based on the statistics of the data summarized in figure 8 superimposed a histogram of 200 tip radii measured on a representative sample.

probability density functions, as shown in figure 9, the larger arrays all converge around 4.8 nm. The distribution is consistent with those obtained from SEM measurements of tips without gates previously reported in Guerrera *et al* [9]. We should add a caveat that the distribution extracted from the *I–V* characteristics would naturally favor a smaller tip radius and perhaps a tighter distribution principally due to the exponential relationship between the field factor (and hence the tip radius) on the emission current.

#### 4. Conclusions

We developed a process for the top-down fabrication of high-aspect-ratio vertically-aligned silicon nanowires embedded in a dielectric matrix, and applied the structures as current limitation elements in silicon field emitter arrays. These field emitter arrays demonstrate excellent performance, with currents  $>1~\mu\text{A}/\text{tip}$  and current densities  $>100~\text{A}~\text{cm}^{-2}$  and a current that scales linearly with the number of emitters in the array, suggesting that the field emitter tips are very uniform. Through numerical modeling of the tip geometry and the field emitter structure we estimated the average nanoscale tip radius and its distribution using electrical characterization of several arrays of field emitters. The arrays have an average emitter tip radius of  $\approx 5~\text{nm}$ , comparable to the state-of-the-art ungated silicon field emitter arrays reported in Guerrera et al [9].

#### **Acknowledgments**

These devices were fabricated in the Microsystems Technology Laboratories, USA. This work was supported by the Defense Advanced Research Projects Agency (Program Manager: Dr Joseph Mangano) and monitored by SPAWAR

(COTR: Israel Perez), SPAWAR award numbers N66001-12-1-4212 and N66001-15-1-4022. The content of this paper does not necessarily reflect the position or the policy of the US Government and no official endorsement of the US Government should be inferred.

#### References

- [1] Brönstrup G, Jahr N, Leiterer C, Csáki A, Fritzsche W and Christiansen S 2010 Optical properties of individual silicon nanowires for photonic devices ACS Nano 4 7113–22

- [2] Gunasundari E, Senthilnathan K, Sivabalan S, Nakkeeran K and Babu P R 2013 Silicon nanowire embedded circular photonic crystal fiber for nonlinear applications 2013 Int. Conf. on Advanced Nanomaterials and Emerging Engineering Technologies (ICANMEET) pp 524–6

- [3] Ramos D, Gil-Santos E, Malvar O, Llorens J M, Pini V, Paulo A S, Calleja M and Tamayo J 2013 Silicon nanowires: where mechanics and optics meet at the nanoscale *Sci. Rep.* 3 3445

- [4] Shiri D, Verma A, Selvakumar C R and Anantram M P 2012 Reversible modulation of spontaneous emission by strain in silicon nanowires Sci. Rep. 2 461

- [5] Duan X, Huang Y, Agarwal R and Lieber C M 2003 Single-nanowire electrically driven lasers *Nature* 421 241–5

- [6] Goldberger J, Hochbaum A I, Fan R and Yang P 2006 Silicon vertically integrated nanowire field effect transistors *Nano Lett.* 6 973–7

- [7] Cui Y, Zhong Z, Wang D, Wang W U and Lieber C M 2003 High performance silicon nanowire field effect transistors Nano Lett. 3 149–52

- [8] She J C, Deng S Z, Chen J and Xu N S 2004 Field emission properties of ultra-high density vertical aligned silicon nanowires IVNC 2004 Technical Digest of the 17th Int. Vacuum Nanoelectronics Conf., 2004 pp 152–3

- [9] Guerrera S A, Velasquez-Garcia L F and Akinwande A I 2012 Scaling of high-aspect-ratio current limiters for the individual ballasting of large arrays of field emitters *IEEE Trans. Electron Devices* 59 2524–30

- [10] Velasquez-Garcia L F, Guerrera S A, Niu Y and Akinwande A I 2011 Uniform high-current cathodes using massive arrays of Si field emitters individually controlled by vertical Si ungated FETs: 1. Device design and simulation IEEE Trans. Electron Devices 58 1775–82

- [11] Palmer D, Gray H F, Mancusi J, Temple D, Ball C, Shaw J L and McGuire G E 1995 Silicon field emitter arrays with low capacitance and improved transconductance for microwave amplifier applications *J. Vac. Sci. Technol.* B 13 576–9

- [12] Spindt C A, Holland C E, Rosengreen A and Brodie I 1993 Field-emitter-array development for high-frequency operation J. Vac. Sci. Technol. B 11 468–73

- [13] Browning J, McGruer N E, Meassick S, Chan C, Bintz W J and Gilmore M 1992 Gate field emitter failures: experiment and theory *IEEE Trans. Plasma Sci.* 20 499–506

- [14] Browning J, McGruer N E, Bintz W J and Gilmore M 1992 Experimental observations of gated field emitter failures IEEE Electron Device Lett. 13 167–9

- [15] Temple D, Ball C A, Palmer W D, Yadon L N, Vellenga D, Mancusi J, McGuire G E and Gray H F 1995 Fabrication of column-based silicon field emitter arrays for enhanced performance and yield *J. Vac. Sci. Technol.* B 13 150–7

- [16] Solano I, Reichenbach B, Schwoebel P R, Chichester D L, Holland C E, Hertz K L and Brainard J P 2008 Field desorption ion source development for neutron generators Nucl. Instrum. Methods Phys. Res. Sect. Accel. Spectrometers Detect. Assoc. Equip. 587 76–81

- [17] Bargsten Johnson B, Schwoebel P R, Holland C E, Resnick P J, Hertz K L and Chichester D L 2012 Field ion source development for neutron generators Nucl. Instrum. Methods Phys. Res. Sect. Accel. Spectrometers Detect. Assoc. Equip. 663 64–74

- [18] Ellsworth J L, Tang V, Falabella S, Naranjo B and Putterman S 2013 Neutron production using a pyroelectric driven target coupled with a gated field ionization source AIP Conf. Proc. vol 1525 pp 128–32

- [19] McPherson J W, Kim J, Shanware A, Mogul H and Rodriguez J 2003 Trends in the ultimate breakdown strength of high dielectric-constant materials *IEEE Trans. Electron Devices* 50 1771–8

- [20] Verweij J F and Klootwijk J H 1996 Dielectric breakdown I: A review of oxide breakdown Microelectron. J. 27 611–22

- [21] Takemura H, Tomihari Y, Furutake N, Matsuno F, Yoshiki M, Takada N, Okamoto A and Miyano S 1997 A novel vertical current limiter fabricated with a deep trench forming technology for highly reliable field emitter arrays *IEEE Int. Electron Devices Meeting, IEDM'97. Tech. Dig.* pp 709–12

- [22] Akinwande A I, Johnson B R, Holmen J O, Murphy D and Arch D K 1995 Thin-film-edge emitter vacuum microelectronics devices for lamp/backlight applications Int. Vacuum Microelectronics Conf., 1995. IVMC., pp 418–22

- [23] Velasquez-Garcia L F, Guerrera S A, Niu Y and Akinwande A I 2011 Uniform high-current cathodes using massive arrays of Si field emitters individually controlled by vertical Si ungated FETs: 2. Device fabrication and characterization *IEEE Trans. Electron Devices* 58 1783–91

- [24] Holland C E 2013 private communication

- [25] Marcus R B, Ravi T S, Gmitter T, Chin K, Liu D, Orvis W J, Ciarlo D R, Hunt C E and Trujillo J 1990 Formation of silicon tips with <1 nm radius Appl. Phys. Lett. 56 236

- [26] Hong C-Y 2003 Intelligent field emission arrays *Thesis* Massachusetts Institute of Technology (http://hdl.handle. net/1721.1/17037)

- [27] Hong C-Y and Akinwande A I 2005 Oxidation sharpening mechanism for silicon tip formation *Electrochem. Solid-State Lett.* 8 F13–5

- [28] EerNisse E P 1977 Viscous flow of thermal SiO<sub>2</sub> Appl. Phys. Lett. **30** 290–3

- [29] Guerrera S A and Akinwande A I 2013 Self-aligned, gated field emitter arrays with integrated high-aspect-ratio current limiters 26th Int. Vacuum Nanoelectronics Conf. (IVNC) pp 1–2

- [30] Kamins T 1988 *Structure* Polycrystalline silicon for integrated circuit applications (US: Springer) pp 41–89

- [31] Kamins T I, Mandurah M M and Saraswat K C 1978 Structure and stability of low pressure chemically vapor-deposited silicon films J. Electrochem. Soc. 125 927–32

- [32] Spindt C A, Brodie I, Humphrey L and Westerberg E R 1976 Physical properties of thin-film field emission cathodes with molybdenum cones J. Appl. Phys. 47 5248–63

- [33] Patterson A A and Akinwande A I 2013 Elementary framework for cold field emission: incorporation of quantum-confinement effects *J. Appl. Phys.* **114** 234303

- [34] Child C D 1911 Discharge from hot CaO *Phys. Rev. Ser.* I **32** 492–511

- [35] Whaley D R, Duggal R, Armstrong C M, Bellew C L, Holland C E and Spindt C A 2008 Operation of

- a low-voltage high-transconductance field emitter array TWT *IEEE Int. Vacuum Electronics Conf., IVEC 2008* pp 78–9

- [36] Ding M, Sha G and Akinwande A I 2002 Silicon field emission arrays with atomically sharp tips: turn-on voltage and the effect of tip radius distribution *IEEE Trans. Electron Devices* **49** 2333–42

- [37] Dvorson L, Ding M and Akinwande A I 2001 Analytical electrostatic model of silicon conical field emitters. I *IEEE Trans. Electron Devices* **48** 134–43

- [38] Jensen K L, Zaidman E G, Kodis M A, Goplen B and Smithe D N 1996 Analytical and seminumerical models for gated field emitter arrays. I. Theory J. Vac. Sci. Technol. B 14 1942–6