Abstract

CMOS miniaturization is now approaching the sub-10 nm level, and further downscaling is expected. This size scaling will end sooner or later, however, because the typical size is approaching the atomic distance level in crystalline Si. In addition, it is said that electron transport in FETs is ballistic or nearly ballistic, which means that the injection velocity at the virtual source is a physical parameter relevant for estimating the driving current. Channel-materials with higher carrier mobility than Si are nonetheless needed, and the carrier mobility in the channels is a parameter important with regard to increasing the injection velocity. Although the density of states in the channel has not been discussed often, it too is relevant for estimating the channel current. Both the mobility and the density of states are in principle related to the effective mass of the carrier. From this device physics viewpoint, we expect germanium (Ge) CMOS to be promising for scaling beyond the Si CMOS limit because the bulk mobility values of electrons and holes in Ge are much higher than those of electrons and holes in Si, and the electron effective mass in Ge is not much less than that in III–V compounds. There is a debate that Ge should be used for p-MOSFETs and III–V compounds for n-MOSFETs, but considering that the variability or nonuniformity of the FET performance in today's CMOS LSIs is a big challenge, it seems that much more attention should be paid to the simplicity of the material design and of the processing steps. Nevertheless, Ge faces a number of challenges even in case that only the FET level is concerned. One of the big problems with Ge CMOS technology has been its poor performance in n-MOSFETs. While the hole mobility in p-FETs has been improved, the electron mobility in the inversion layer of Ge FETs remains a serious concern. If this is due to the inherent properties of Ge, only p-MOSFETs might be used for device applications. To make Ge CMOS devices practically viable, we need to understand why electron mobility is severely degraded in the inversion layer in Ge n-channel MOSFETs and to find out how it can be increased. In the Si CMOS technology, the SiO2/Si interface has long been investigated and cannot be ignored even after the introduction of high-k gate stack technology. In that sense, the GeO2/Ge interface should be intensively studied to make the best of Ge's advantages. Therefore we first discuss the GeO2/Ge interface with regard to its physical and electrical characteristics. When we regard Ge as a channel material beyond Si for high performance ULSIs, we also have to seriously consider the gate stack scalability and reliability. The source/drain engineering, as well as the gate stack formation, is another challenge in Ge MOSFET design. Both the higher metal/Ge contact resistance and the larger p/n junction leakage current may be the consequences of Ge's intrinsic properties because they are derived from the strong Fermi-level pinning and the narrow energy band gap, respectively. Even if the carrier transport in the channel may be ideally ballistic, these properties should degrade FET properties. The narrower energy band gap of Ge is often addressed, but the higher dielectric constant of Ge is rarely discussed. This is also the case for most of the other high-mobility materials. The dielectric constant is directly and negatively related to short-channel effects, and we have not been able to provide a substantial solution to overcome this hardship. We have to keep this in mind for the short-channel FET operation. Although a number of problems remain to be solved, in this paper, we view the current status of Ge FET technology positively. A number of (but not all) Ge-related challenges have been overcome in the past 10 years, which seems to be a good time to summarize the status of Ge technology, particularly materials engineering aspects rather than device integration issues. Since we cannot cover all of the results published to date, we mainly discuss fundamental aspects based on our experimental results. Remaining challenges are also addressed but not comprehensively. Integration issues are not discussed in this review. Finally, new types of electron devices utilizing Ge's advantages are briefly introduced on the basis of our experimental results.

Export citation and abstract BibTeX RIS

Table of contents

1. Introduction

2. Stabilizing GeO2/Ge gate stacks

2.1 Thermodynamics and kinetics of GeO desorption

2.2 Thermodynamic approach

2.2.1 High-pressure O2 oxidation

2.2.2 GeO2/Ge MOS capacitors

2.2.3 Defects in bulk GeO2

2.3 Kinetic approach

2.4 Materials approach

2.5 Oxidation kinetics of Ge

3. Enhancing electron mobility in Ge MOSFETs

3.1 Dit reduction

3.2 Substrate surface orientation

3.3 Atomically flat Ge surface

3.4 Defects in Ge substrate

4. Scaling EOT

4.1 Low-temperature high-pressure O2 oxidation

4.2 Low-oxygen-potential oxides

4.3 High-k material selection for further EOT scaling

5. Assuring Ge gate stack reliability

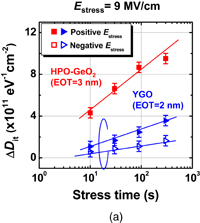

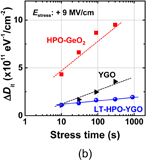

5.1 Initial traps and trap generation

5.2 Network flexibility and rigidity

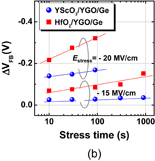

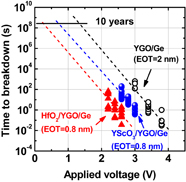

5.3 Reliable scaled Ge gate stacks

6. Reducing contact resistance and junction leakage

6.1 Schottky barrier height control

6.1.1 Fermi-level pinning modulation: tunnel contact

6.1.2 Fermi-level pinning modulation: electron density tuning in metals

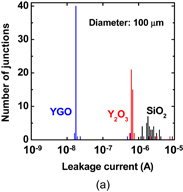

6.2 n+/p junction

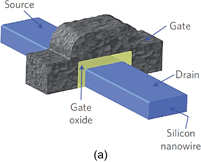

7. Setting new devices

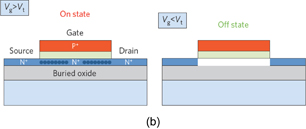

7.1 ET-GeOI FET

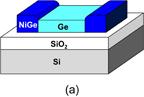

7.2 Metal source/drain FET

7.3 Junctionless FET

7.4 New field effect on Ge

8. Conclusions and future outlook

1. Introduction

Si CMOS miniaturization is currently approaching the 7 nm node not in a single FET operation but in the integration level.1,2) Nevertheless, planar FET size scaling including FinFET will eventually end because there is a physical limit of the distance between neighboring atoms, so FET performances have to be improved by other ways. System performance will be improved by using three-dimensional rather than two-dimensional integration, and high-mobility channel semiconductors have always been desired for high-speed and/or low-power applications. It is, however, not easy to implement new materials in the current Si-LSIs. Furthermore, FET performance will be limited by the ballistic transport in the channel, and the ultimate carrier speed will depend on the injection velocity near the source side.3,4) Whether the ultimate performance of FETs is related to the carrier mobility or not is often discussed, and here, we note that the injection velocity is related to the mobility because both properties depend on the carrier's effective mass. It has been shown experimentally that a higher mobility is needed to achieve a higher injection velocity.5)

Various materials have been proposed for high-mobility channels beyond Si. Look at the bulk electron and hole mobility values in Table I. Note that germanium (Ge) shows the most balanced electron and hole mobility values. The monoatomic semiconductor nature of Ge should also be emphasized because the characteristics of a compound semiconductor are rather sensitive to its stoichiometry. The density of states in the channel is also relevant for estimating the channel current because it is directly related to the gate capacitance.6) Both the density of states and high mobility in the channel are related to the effective mass of the carriers. From this device physics viewpoint, we expect that Ge CMOS is most promising for "beyond Si-CMOS" scaling. On the other hand, it has been said that Ge should be used for p-MOSFETs and III–V compounds for n-MOSFETs.7,8) In fact, a critical technology selection according to the applications might be needed, but when it is considered that a big challenge in the current CMOS LSIs comes from the variability or nonuniformity of the FET performance in them, it seems that much more attention should be paid to the simplicity of the material design and of the processing steps.

Table I. Carrier mobility, effective mass and energy band gap in bulk Si, Ge, and typical III–V compound semiconductors. A very high hole mobility in Ge is far ahead of others.

| Si | Ge | GaAs | InP | InAs | InSb | |

|---|---|---|---|---|---|---|

| Electron mobility (cm2 V−1 s−1) | 1600 | 3900 | 9200 | 5400 | 40000 | 77000 |

| Electron effective mass (/m0) | mt: 0.19 ml: 0.916 | mt: 0.082 ml: 1.467 | 0.067 | 0.082 | 0.023 | 0.014 |

| Hole mobility (cm2 V−1 s−1) | 430 | 1900 | 400 | 200 | 500 | 850 |

| Hole effective mass (/m0) | mHH: 0.49 mLH: 0.16 | mHH: 0.28 mLH: 0.044 | mHH: 0.45 mLH: 0.082 | mHH: 0.45 mLH: 0.12 | mHH: 0.57 mLH: 0.35 | mHH: 0.44 mLH: 0.016 |

| Energy band gap (eV) | 1.12 | 0.66 | 1.42 | 1.34 | 0.36 | 0.17 |

A number of research outputs on Ge have been so far reported and both its advantages and disadvantages have been discussed considerably.9,10) Although our objective is to realize high-performance Ge CMOS LSIs with a realistic shape, Si CMOS LSIs will not disappear and new Ge devices will coexist with Si devices. New materials might thus not necessarily be used for all of the functions in LSIs, but the total system performance should be improved by using their advantageous aspects. If the advantages of Ge are not exploited, Ge will lose its original appeal.

Germanium was discovered in 1886 by Winkler,11) the first transistor was demonstrated on Ge in 1947 by Bardeen, Brattain, and Shockley,12) and the first integrated circuit (IC) was demonstrated on Ge in 1958 by Kilby.13) The electric properties of Ge were reported in depth approximately 100 years ago.14) Thus Ge is obviously not a new electron-device material but has been "sleeping" for half a century even though there have of course been strong demands for nuclear radiation spectrometers and IR detectors. Now, it is waking up from its long sleep and is attracting much attention. Although there might be a number of apparently intrinsic challenges, for most of them, we may find solutions on the basis of present in-depth understandings of materials science and device physics. This optimistic view is held throughout this paper.

Nevertheless, we have to remind ourselves what problems there were in the past before the Si era. Historical details of Ge and Si research in the early stage of electron device research and development are interestingly described in Ref. 15, which points out several reasons that Si has become the mainstream material for electron devices.

- (i)Si is abundant on Earth.

- (ii)The operation temperature range is wider in Si than in Ge.

- (iii)Purer crystals can be obtained in Si than in Ge.

- (iv)Single crystalline Si is produced on an industrial scale.

- (v)SiO2 is a very stable material for the surface passivation.

It is easily understandable that those reasons were critical for the successful production of reliable devices. Conversely speaking, they are problems that must be solved if Ge is to overcome Si. Since (i) and (ii) are owing to inherent properties (Clarke number and energy band gap), it seems impossible to solve them. However, Ge is not a rare material and it should be used only in parts of devices where it is advantageous rather than for all purposes. We should keep in mind that a high junction leakage current is potentially a big concern in any devices even at room temperature. (iii) is related to defect control in the Ge crystallinity. This is a big concern in ULSI, but the crystal purity has been improved a lot. (iv) is related to how to use Ge. Since it is now considered that Si will be used as the bottom substrate, the possible wafer size of Ge is not necessarily a big concern. (v) is still a serious challenge in the device fabrication process because we know that a key to fabricating high-performance FETs is understanding how to control any hetero interfaces. As discussed later, GeO2 is not stable, which was well known and investigated even before the Si era,16) and we cannot simply mimic the successful SiO2/Si technology. Thus, Ge gate stack and passivation technologies should be studied deeply and carefully when Ge is considered for use as a "beyond Si" channel material.

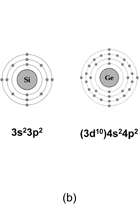

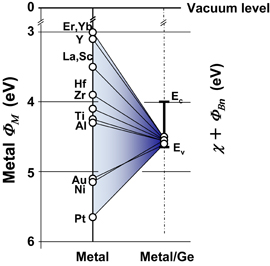

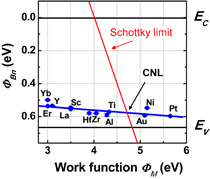

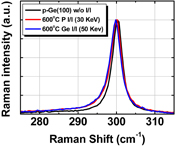

Let us start here by showing some general material properties of Ge. Figure 1(a) shows the electronic structure of Ge, which is fundamental for considering device physics. In addition to the band gap being narrower than that of Si, the direct band gap at the Γ-point is significantly smaller in Ge than in Si. This is very important for the optical applications of Ge. It is interesting to see the difference between the electron configurations of Si and Ge atoms as shown in Fig. 1(b). In fact, 3d electrons in Ge affect the energy levels of 4s and 4p electrons and the 4s electron level is rather deep because 3d electrons cannot fully screen the inner shell. The Clarke number of Ge shows that Ge is the 43rd most abundant element on Earth, whereas Si is the second most abundant. Ge has several kinds of isotopes with different mass numbers, and they are discussed later in the context of marker experiments. The material properties of Ge are summarized in Table II, where they are compared with those of Si.

Download figure:

Standard image High-resolution imageFig. 1. (a) Electronic structure of Ge. The conduction band minimum is located at L-point with an indirect energy band gap of 0.66 eV. The direct energy band gap at the Γ-point is about 0.80 eV, which is rather close to the indirect one. This is in striking contrast to the Si case. (b) Schematic electron configurations of Si and Ge atoms. The 4s state of Ge is rather deep compared with the 3s state of Si because of the insufficient screening by 3d electrons.

Download figure:

Standard image High-resolution imageTable II. Typical material properties of Ge and Si. All of them listed in this table in addition to carrier mobility should be considered for designing real electron devices.

| Ge | Si | |

|---|---|---|

| Density (g/cm3) | 5.327 | 2.328 |

| Young's modulus (N/m2) 〈100〉 direction | 1.3 × 1011 | 1 × 1011 |

| Thermal conductivity (W cm−1 K−1) at 300 K | 0.6 | 1.5 |

| Dielectric constant | 16.0 | 11.9 |

| Refractive index at 633 nm | 5.48 | 3.88 |

| Lattice constant (Å) | 5.64613 | 5.43095 |

| Clarke number (%) | 0.00065 | 25.8 |

This review consists of eight sections, but by and large, it can be divided into two parts. The first part is on the gate stacks. Ge oxidation stabilizing the Ge interface is discussed in Sect. 2 because GeO2/Ge is the basis for Ge gate stacks. Through this investigation, a big difference between the oxidation processes of Ge and Si is discussed thermodynamically. On the basis of this understanding, markedly improved Ge MOS capacitor characteristics are presented. In addition, high-performance n-channel Ge FET properties that will make high-performance Ge CMOS devices possible are demonstrated in Sect. 3. This part naturally extends to cover the high-k/Ge systems needed to meet the scalability requirements discussed in Sect. 4. Furthermore, the assurance of gate stack reliability is needed for the practical application of Ge devices. This will be discussed in Sect. 5 by introducing a new reliability concept. The second part of this review is on the source/drain formation, including metal/Ge contact. This formation process is still under investigation, but we would like to share our views about this issue. In particular, the very strong Fermi-level pinning (FLP) in metal/Ge contacts is unique to Ge and is discussed in Sect. 6. The final section discusses new types of devices exploiting specific advantages of Ge. Although the Roadmap issues17) are often discussed extensively in the introductory part of review papers, in this review, we instead focus on the material aspects of the Ge CMOS process and device technology.

We would like to present our views, based on material properties and thermodynamic considerations, concerning mainly both how to improve Ge gate stacks and how to control the perfect FLP on Ge by material science based engineering. Of course, there may be other ways to obtaining high-performance Ge FETs, but we hope that guidelines based on the material and thermodynamic aspects considered in this paper will be useful to anyone working on Ge or new channel materials.

2. Stabilizing GeO2/Ge gate stacks

First let us discuss how to achieve excellent Ge gate stacks with GeO2/Ge without considering any other concerns such as scalability or reliability. We should pay attention to the GeO2/Ge interface because the SiO2/Si interface is still the heart of Si-CMOS gate stack technology even after metal gate/high-k gate stacks have been introduced.

The parabolic law of the thermal oxidation for Ge was also reported18,19) as the Deal–Grove model for Si,20) but this does not mean that GeO2/Ge might be the same as SiO2/Si. This is not the point for achieving wonderful gate stacks. Although the Ge oxidation kinetics will be discussed later, a big difference between the device-process technology for Ge and that for Si is that significant GeO desorption from the GeO2/Ge stack should be taken into consideration.21) On the other hand, high-temperature oxidation is desirable as far as GeO2 quality is concerned because GeO2, like SiO2, has the continuous random network type of structure and the network in the whole film should be completely be stabilized. Understanding and controlling the GeO desorption from the GeO2/Ge stack are therefore of vital importance.

2.1. Thermodynamics and kinetics of GeO desorption

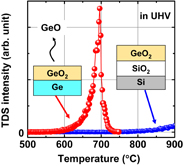

GeO desorption from GeO2 was directly investigated using thermal desorption spectroscopy (TDS) measurements22,23) carried out in ultrahigh vacuum (UHV) at high temperatures,24) because GeO desorption from ultrathin GeO2 on Ge in UHV was reported to occur at temperatures above 400 °C.25) In fact, GeO desorbs from the GeO2/Ge stack at a relatively low temperature but, interestingly, not from GeO2/SiO2 stacks shown in Fig. 2. This indicates that the GeO desorption is directly related to a reaction that triggers GeO desorption at the GeO2/Ge interface.

Fig. 2. Thermal desorption spectra of GeO (m/z = 86, 88, 89, 90, and 92; where m and z are respectively the desorbed species mass and electronic charge) desorbed from GeO2/Ge and GeO2/SiO2/Si stacks in UHV. It is inferred that the GeO desorption is triggered by the GeO2/Ge interface reaction.26)

Download figure:

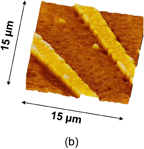

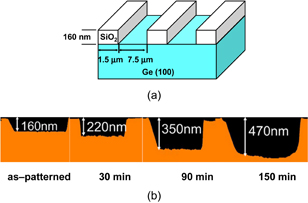

Standard image High-resolution imageFigure 3 shows both (a) schematic cross sections of a GeO2 line-and-space pattern on Ge before and after UHV annealing and (b) the atomic force microscope (AFM) image of the pattern after UHV annealing.26) The Ge substrate is consumed only underneath GeO2 lines, indicating that GeO desorption is caused by a GeO2/Ge reaction. Another aspect of the GeO desorption is shown in Fig. 4, where (a) is a schematic image of a SiO2 line-and-space pattern on Ge before N2 annealing and (b) shows AFM cross-sectional images of the pattern before and after N2 annealing at 600 °C.26) Since N2 gas actually included a small amount of O2, Ge was consumed only where it was not under SiO2. This is a typical example of the active oxidation.

Download figure:

Standard image High-resolution imageFig. 3. (a) Schematic images of a line-and-space patterned GeO2 on Ge expected before and after annealing in UHV. Ge covered with GeO2 is only consumed in UHV-PDA. (b) Top-view AFM image of GeO2/Ge after annealing in UHV. This result clearly shows that GeO desorption is induced by the reaction of GeO2 with Ge.26)

Download figure:

Standard image High-resolution imageFig. 4. (a) Schematic image of a line-and-space patterned SiO2 on Ge. (b) Cross-sectional height profiles inspected by AFM of samples as-patterned and annealed at 600 °C in N2 for 30, 90, and 150 min. Ge is etched by the remaining O2 in N2, which is a typical example of active oxidation.26)

Download figure:

Standard image High-resolution imageConsidering that GeO desorption is associated with the reaction at GeO2/Ge as shown above, we suggest the following net reaction.

Next, let us think about what is the difference between Ge oxidation and Si oxidation thermodynamically. Vapor pressures of the volatile species Ge(g), GeO(g), and GeO2(g) in the Ge-and-O2 system as well as their Si counterparts in the Si-and-O2 system under a thermodynamic equilibrium condition27) were first calculated using a thermodynamic database.28) The equilibrium vapor pressures of GeO(g), GeO2(g), and Ge(g) (p-GeO, p-GeO2, and p-Ge, respectively) are shown in Fig. 5(a) as a function of the p-O2 at 550 °C. Similar reactions were calculated for Si at 900 °C, as shown in Fig. 5(b). The Si results are the same as reported elsewhere.29) Note that the system temperatures for both Ge and Si were ∼0.7 × TM (TM; melting temperature), which are typical temperatures used for the dry oxidation of these semiconductors. At p-O2 < 10−26.3 atm, GeO(g), GeO2(g), and Ge(g) equilibrate with Ge(s) in the following reactions.

GeO(g) and GeO2(g) equilibrate with GeO2(s) at p-O2 > 10−26.3 atm.

Three important points in Fig. 5 are the following:

- (i)p-GeO is the highest at the GeO2/Ge interface up to p-O2 ∼ 1 atm,

- (ii)p-GeO has a negative slope against p-O2, and

- (iii)p-GeO is comparable with p-GeO2 at p-O2 ∼ 1 atm.

Looking at the p-O2 ∼ 1 atm region in Fig. 5(a), one clearly sees that the p-GeO is much higher than that of SiO in Fig. 5(b), in addition to (iii). This means that GeO desorption from GeO2/Ge observed experimentally is thermodynamically reasonable. Furthermore, a negative slope of p-GeO against p-O2 suggests that GeO desorption from the surface may affect the region deep inside GeO2 film and degrade both bulk and interface of GeO2/Ge system. On the other hand, since p-GeO decreases with increase in p-O2, the high-pressure O2 oxidation might be effective for growing SiO2-like GeO2, which is discussed in the next section.

Download figure:

Standard image High-resolution imageFig. 5. (a) Equilibrium vapor pressure of GeO(g), GeO2(g), and Ge(g) at 550 °C as a function of O2 pressure (p-O2). (b) Equilibrium vapor pressure of SiO(g), SiO2(g), and Si(g) at 900 °C as a function of p-O2. 550 °C is 0.7 × TM(Ge) and 900 °C is 0.7 × TM(Si), where TM(Ge) and TM(Si) are the melting temperatures of Ge and Si, respectively. It is noted that 550 and 900 °C are also typical oxidation temperatures for Ge and Si, respectively. At p-O2 = 1 atm, the vapor pressure of GeO is significantly higher than that of SiO.27)

Download figure:

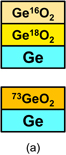

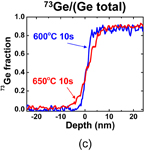

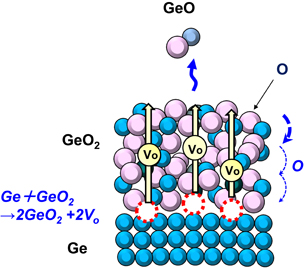

Standard image High-resolution imageNext, the GeO desorption kinetics is experimentally discussed. As shown in Fig. 6, the temperature giving a peak in TDS increases with the GeO2 thickness increase, while it little depends on how GeO2 is formed.30) This fact suggests that the GeO desorption is limited by diffusion through the bulk GeO2 network. It might be, however, unlikely that GeO is the diffusion species. To clarify the diffusion species and mechanism, isotope tracing experiments using 18O and 73Ge were carried out with TDS and secondary ion mass spectroscopy (SIMS).30) 73Ge was used for these experiments because it is an only Ge isotope with an odd mass number and thus easier to trace in the marker experiments. Two kinds of gate stack structures focusing on 18O and 73Ge were prepared, as shown in Fig. 7(a). The Ge16O is desorbed at a lower temperature, as shown in Fig. 7(b), which suggests that O of desorbed GeO is not from the interface but from the top layer. It was also suggested that Ge of desorbed GeO was also from the top layer (data not shown). Results point out that both Ge and O are desorbed from the top surface of GeO2 at the initial stage in the temperature sweep. This initial desorption from the top layer seems inconsistent with GeO desorption being triggered by the GeO2/Ge reaction as discussed previously. However, it is understandable by considering that the oxygen atom diffuses from the top layer toward the interface, namely, oxygen vacancy (Vo) diffusion from the GeO2/Ge interface to the top surface. To determine the actual diffusion species through the GeO2 film, the sample structure shown in Fig. 8(a) was prepared using both 73Ge and 18O, and then annealed at 600 and 650 °C. Figures 8(b) and 8(c) show that the O atom is the dominant diffusion species in GeO2.30) It is actually regarded that Vo is formed through the reaction at the interface,

Namely, the Ge substrate is oxidized by GeO2 at the interface, while at the surface,

In the net reaction,

The Vo formation triggered by the oxidation in (2.4) drives GeO desorption through the Vo diffusion.30) Figure 9 is more intuitively helpful to understand what occurs inside the GeO2 film on a Ge substrate. This kinetic view is the key concept when we treat GeO2/Ge gate stacks.

Download figure:

Standard image High-resolution imageFig. 6. (a) TDS intensity of GeO (m/z = 86, 88, 89, 90, and 92) desorbed from sputtered GeO2 on Ge stacks with various GeO2 thicknesses. A thinner GeO2 on Ge shows a lower desorption temperature. (b) Peak desorption temperature in TDS as a function of initial thickness of differently grown GeO2. There is no considerable difference of GeO desorption temperature for GeO2 grown differently on Ge. This fact suggests that a diffusion process in GeO2 is not through a pin-hole but occurs uniformly in the GeO2 film.23,26)

Download figure:

Standard image High-resolution imageDownload figure:

Standard image High-resolution imageFig. 7. (a) Schematics of sample structures used in the isotope tracing experiments investigating GeO desorption. Two types of samples were prepared using 18O and 73Ge. (b) Typical TDS results of GeO from Ge16O2/Ge18O2/Ge. Each GeO2 thickness was ∼17 nm. Ge16O was interestingly observed at lower temperature than Ge18O existing at the interface. In case of 73GeO2/Ge, 73GeO was detected at lower temperature, though the reaction should occur at the interface (data not shown for the 73GeO desorption).

Download figure:

Standard image High-resolution imageDownload figure:

Standard image High-resolution imageDownload figure:

Standard image High-resolution imageFig. 8. (a) Schematic sample structure for determining the diffusion species through GeO2. SIMS profiles of (b) 18O and (c) 73Ge in the sample annealed at 600 and 650 °C in N2. The O atom is the dominant diffusion species in GeO2 at around 600 °C.30)

Download figure:

Standard image High-resolution imageFig. 9. A kinetic model proposed for the GeO desorption. For understanding the above experimental results, it is most probable that Vo diffusion from the GeO2/Ge interface triggers GeO desorption at the top surface.30) It is uncertain whether the oxygen vacancy Vo in amorphous GeO2 can be well defined, but we will use the Vo although it might be slightly different from Vo in crystalline materials.

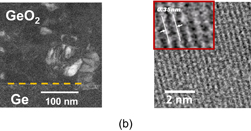

Download figure:

Standard image High-resolution imageGeO2 film properties were affected by UHV annealing through the above process. Figures 10(a) (X-ray diffraction, XRD) and 10(b) (transmission electron microscope, TEM)31) show that GeO2 on Ge in UHV-annealing at 660 °C is crystallized to an α-quartz type structure.32) This is also understandable by considering the reduction in the crystallization barrier energy with the help of the Vo diffusion in GeO2. This seems quite interesting from the viewpoint that Vo's make the continuous random network (CRN) type of GeO2 structure unstable. In fact, if oxygen atom diffusion can follow the Vo diffusion instantaneously, GeO desorption associated with Vo diffusion may be observed. However, if huge amounts of Vo's are generated under the UHV condition, it is likely that the CRN structure of the GeO2 film may be collapsed and crystallized locally. Those properties in GeO2/Ge are quite different from those in SiO2/Si stacks and, as discussed later, are tightly related to the GeO2 physical properties.

Download figure:

Standard image High-resolution imageFig. 10. (a) XRD patterns of GeO2/Ge(100) and GeO2/SiO2/Si stacks after UHV-PDA at 660 °C for 1 min. 230-nm-thick GeO2 was deposited by rf-sputtering. The former sample was only crystallized to a quartz type of GeO2 in UHV-PDA. (b) Cross-sectional TEM images of GeO2 film on Ge(100) after the UHV-PDA. GeO desorption may help to crystallize GeO2 film.31)

Download figure:

Standard image High-resolution imageBecause oxygen vacancies are always involved both at the interface and in the bulk GeO2, we have to suppress the GeO desorption if we wish to make excellent gate stacks on Ge. There are basically two ways of solving this problem: thermodynamically and kinetically. The kinetic approach was actually carried out first, but we start with discussing the thermodynamic approach, because the thermodynamic one has been more successful and investigated in much more detail. The kinetic one is discussed in Sect. 2.3, after which the material approach combining both of them is discussed in Sect. 2.4.

2.2. Thermodynamic approach

2.2.1. High-pressure O2 oxidation.

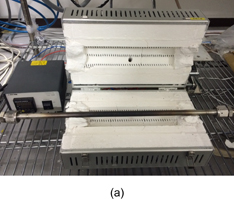

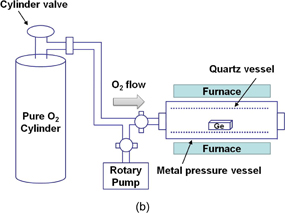

We first tried to form GeO2 thermally under 1 atm O2 but were not satisfied with the results. We naively conjectured that the high-pressure O2 (HPO) oxidation might be effective for suppressing the GeO desorption because we thought enough O2 could reduce the amount of insufficiently oxidized GeOx in the film. Therefore, before considering the thermodynamics of Ge oxidation as described in Sect. 2.1, we carried out the oxidation of Ge in a high-pressure O2 ambient. Since it was not possible to use the conventional quartz furnace for the oxidation at pressures above 10 atm, a stainless chamber with a quartz tube as the inner wall was used for the oxidation as shown in Fig. 11(a). Then, a SUS tube was directly put into the conventional open furnace. The schematic image of the oxidation system is shown in Fig. 11(b). Since it was a very simple system, the actual p-O2 in it could not be directly measured at elevated temperatures. However, because the p-O2 measured after the oxidation was the same as the initial p-O2, only a very slight O2 leakage (if any) in this process was confirmed and the actual p-O2 was estimated according to the Boyle-Charles's law. The p-O2 at the oxidation temperature around 600 °C was estimated from the typical p-O2 of ∼70 atm at room temperature to be roughly 200 atm. p-O2 in this paper is hereafter denoted by the room-temperature p-O2. Although this tube is obviously not suitable for use in the industrial-scale production, we have learned much from these experiments. Very fortunately, in the first HPO experiment, we were able to demonstrate surprisingly good MOS capacitor characteristics with HPO-grown GeO2 on Ge.33) Details of electrical characteristics are discussed in the next section.

Download figure:

Standard image High-resolution imageFig. 11. (a) Photograph of a home-made high-pressure O2 annealing furnace. (b) Schematic image of high-pressure O2 annealing system. Since it is difficult to measure the actual O2 pressure (p-O2) at elevated temperatures, p-O2 at room temperature is referred throughout this paper.

Download figure:

Standard image High-resolution imageLow-temperature HPO of Si at pressures up to 500 atm was reported a couple of decades ago to prepare high-density SiO2 films of sufficient thickness.34) Later, a more practical furnace was used to study the HPO oxidation of Si at pressures up to 10 atm in a quartz tube.35) Although we did not know that high-pressure O2 oxidation of Ge was carried out in the early 80's by Crisman and coworkers,36,37) before our first demonstration of significantly improved capacitance–voltage (C–V) characteristics in HPO-grown GeO2/Ge gate stacks,33) they surprisingly demonstrated Ge gate stack improvement by using very high pressure O2 gas. Therefore, we should appreciate their original work on the HPO oxidation of Ge.

2.2.2. GeO2/Ge MOS capacitors.

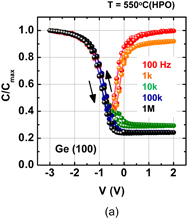

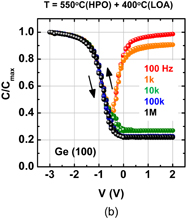

As expected from the thermodynamic consideration discussed previously, the HPO of Ge dramatically improved the Ge MOS capacitor characteristics.38) Furthermore, because the C–V characteristics of HPO-grown GeO2/Ge MOS capacitors showed a slight hysteresis, we tried to annihilate the interface defects by post-oxidation annealing (POA) at a lower temperature (400 °C). This POA was carried out using H2, N2, and O2. As seen when comparing Figs. 12(a) and 12(b), we found that O2 POA at a lower temperature was quite effective in improving C–V characteristics.39) Hereafter, we call it low-temperature oxygen annealing (LOA). The LOA was actually carried out at 400 °C in 1 atm O2 after the formation of high-quality bulk GeO2 by HPO at 550 °C. This process is hereafter called HPO+LOA.

Download figure:

Standard image High-resolution imageFig. 12. Bidirectional C–V characteristics of Au/GeO2/p-Ge(100) MIS capacitors, where GeO2/Ge stacks were fabricated by (a) HPO at 550 °C for 15 min and (b) HPO at 550 °C for 15 min + LOA at 400 °C for 30 min. Although both exhibit good C–V characteristics, the C–V hysteresis is much reduced by adding the LOA.38,39)

Download figure:

Standard image High-resolution imageThe effectiveness of LOA was also thermodynamically justified as follows. Note that the p-GeO at the GeO2/Ge interface is thermodynamically fixed, independent of the p-O2 at a given temperature, because of the Gibbs's phase rule. Interface properties can therefore be further improved, without degrading bulk GeO2 properties, by lowering the temperature. It was actually confirmed by the calculation that p-GeO was decreased by lowering the temperature in 1 atm O2.27) This means that improving MOS C–V characteristics by LOA in Fig. 12(b) is thermodynamically reasonable. Thus, it is concluded with confidence that the wonderful MOS gate stacks on Ge can be made by suppressing the GeO desorption from GeO2/Ge gate stacks.

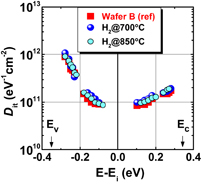

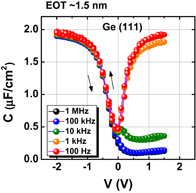

Next, we quantify how the interface is improved by estimating the interface state density Dit. Those who are not familiar with the C–V characteristics of Ge MOS capacitors might think that the minority carrier response in the inversion region at low frequencies in Fig. 12 is huge and that Dit should be high. This is not true. It is due to the intrinsic bulk minority carrier response in the Ge bulk with the narrower energy band gap. This means that characterization methods usually available for estimating the Dit in Si MOS capacitors cannot be used in Ge cases. For example, the conductance method in which the minority carrier capture and emission only from interface states are assumed40) is widely used for estimating the Dit spectrum in Si MOS capacitors quantitatively. In the C–V characterization of Ge MOS capacitors, however, the bulk minority carrier generation needs to be taken into account. Therefore, if we apply the normal conductance method to Ge MOS capacitors at room temperature, we would have a big error in the Dit estimation. There are two ways to overcome this difficulty. One is to lower the measurement temperature, because lowering the temperature must reduce the minority carrier generation in the bulk exponentially. The other is to develop a new equivalent circuit model to describe Ge MOS capacitor characteristics at room temperature. The equivalent circuit was carefully developed by Fukuda et al.41) and Martens et al.42) We employed the former method because it was experimentally straightforward.

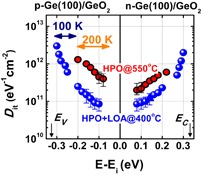

Figure 13 shows Dit profiles estimated by the conductance method. They are the profiles estimated at 200 and 100 K in MOS capacitors with GeO2/Ge(100) grown both by HPO and by HPO+LOA. The midgap Dit is on the order of 1010 cm−2 eV−1 in HPO+LOA,39) which is to our knowledge the lowest of midgap Dit values so far reported for Ge gate stacks. Note that forming gas annealing (FGA) was not employed for reducing Dit. The reason why the oxidation process can make Ge interface quality so remarkable may be that Ge–O bonds at the GeO2/Ge interface are more flexible than Si–O bonds at the SiO2/Si interface. Therefore we regard the LOA as the self-passivation of the GeO2/Ge interface by oxygen itself rather than H2 gas in FGA. The effectiveness of aforementioned oxidation process may also be understandable in conjunction with the viscoelastic properties of GeO2.43)

Fig. 13. Energy distributions of Dit inside the energy band gap, estimated by the low-temperature conductance method at 200 and 100 K for two kinds of Au/GeO2/p-Ge(100) capacitors. GeO2 films were grown by HPO and by HPO+LOA. Ei is the midgap position in the energy band gap. Both Dit profiles exhibit the so-called U-shape distributions inside the energy band gap. Dit values are much lower in the HPO+LOA case, and the midgap Dit in HPO+LOA is below 1011 cm−2 eV−1, without any passivation process.39)

Download figure:

Standard image High-resolution imageThe FGA effect on GeO2/Ge interfaces is still under debate in related conferences. Our experiments have never shown any Dit improvements in the FGA, although annealing temperature effects have been observed occasionally. It was also reported that H-terminated Ge(100) was unstable.44) However, hydrogen is a tricky atom, so we need to carefully investigate it in more detail, including deuterium or radical effects.45)

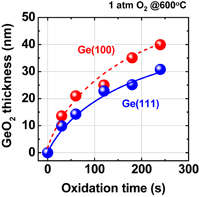

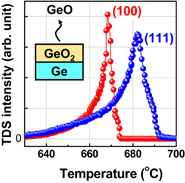

The surface orientation of the substrate is always an issue in surface channel FETs in terms of both process stability and carrier mobility. Since the carrier mobility is discussed in Sect. 3.2, the process sensitivity and MOS capacitor characteristics are addressed here. The oxidation rates of Ge(100) and (111) under 1 atm O2 at 600 °C are shown in Fig. 14 as a function of oxidation time. The oxidation rate of Ge(111) is much lower than that of (100).39) This suggests that Ge(111) would be better in terms of GeO2 scalability as the interfacial layer of high-k dielectric film. Furthermore, the substrate orientation dependence of the GeO desorption was also investigated after depositing 30-nm-thick GeO2 on Ge(100) and (111) wafers. Figure 15 shows that the GeO desorption temperature is much higher on (111) than on (100),30) and these results strongly suggest that Ge(111) is superior to Ge(100) with regard to the rate of GeO desorption under a given process condition. Concerning the interface, no significant Dit difference between Ge(100) and Ge(111) was observed when examining the C–V characteristics of MOS capacitors made using the HPO+LOA process.39)

Fig. 14. GeO2 thickness on Ge(100) and (111) surfaces grown in 1 atm O2 at 600 °C is plotted as a function of oxidation time. Ge(111) has a lower oxidation rate.39)

Download figure:

Standard image High-resolution imageFig. 15. TDS results for GeO desorbing from 30-nm-thick GeO2 on Ge(100) and (111) are shown. Ge(111) is more robust against GeO desorption.30)

Download figure:

Standard image High-resolution image2.2.3. Defects in bulk GeO2.

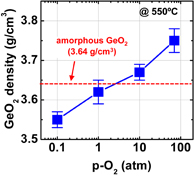

Note that the quality of not only the interface but also the bulk GeO2 film grown in HPO is greatly improved. Figure 16 shows that (a) the water etching rate is slightly less in HPO-GeO2 and that (b) C–V hysteresis increases with the time left in the air more clearly in APO-GeO2 (APO: atmospheric pressure O2) than in HPO-GeO2. These facts indicate that the HPO process densifies the GeO2 film and reduces the amount of electrical traps in it. The density increase of HPO-GeO2 directly detected by the grazing incident X-ray reflectivity (GIXR) measurement is shown in Fig. 17.46)

Download figure:

Standard image High-resolution imageFig. 16. (a) Etching rate of HPO- and APO-grown GeO2 films by alcohol-diluted H2O. HPO-grown GeO2 is more tolerant against H2O etching than APO-grown GeO2. (b) Relationship between air exposure time and the C–V hysteresis in HPO+LOA and APO+LOA GeO2/Ge stacks. HPO+LOA samples are clearly more robust with regard to their C–V hysteresis.

Download figure:

Standard image High-resolution imageFig. 17. Density of GeO2 film estimated by GIXR as a function of oxygen pressure p-O2. The density of the GeO2 film oxidized at 550 °C clearly increases with increasing p-O2. Note that p-O2 plotted here is the O2 pressure at room temperature.46) No density change has been reported for SiO2 in HPO oxidation of Si.35)

Download figure:

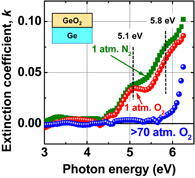

Standard image High-resolution imageWe suspect that APO-grown GeO2 films may have Vo-induced voids in it. Figure 18 shows the impact of PDA on GeO2 film properties, evaluated by the band-edge photo-absorption with spectroscopic ellipsometry.23) An appreciable subgap (band edge tailing) formation is observed in N2- or APO-PDA cases but not in HPO-PDA. The optical band gap of HPO-GeO2 is estimated to be ∼6.0 eV. This suggests that the subgap formation may be related to oxygen deficiency in the GeO2 film. Looking at the spectra more carefully, one can see that the subgap absorption seems to consist of two peaks at ∼5.1 and ∼5.8 eV. Those peaks might be correlated with defects such as neutral O vacancies or Ge2+, which was reported as a plausible origin of ∼5 eV photo-absorption observed in oxygen-deficient GeO2 bulk glass.47) Furthermore, subgap formation was not detected in GeO2 deposited on SiO2 (data not shown). Therefore, the oxygen deficiency is closely related with the interface reaction discussed in Sect. 2.1.

Fig. 18. Extinction coefficient of sputtered GeO2 film on Ge(100) after annealing in N2, 1 atm O2 and HPO at 600 °C, inspected by the spectroscopic ellipsometry. The absorption tail around 5–6 eV appears by annealing in both 1 atm N2 and O2, while no tailing is observed in HPO annealing.23)

Download figure:

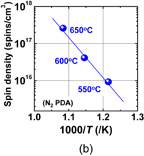

Standard image High-resolution imageElectron spin resonance (ESR) studies were also carried out to detect defects in the GeO2/Ge stack.31) Figure 19(a) shows that almost no signals are detected in case of HPO-annealed GeO2 on Ge, while bulk defect signals in other cases are clearly observed. The annealing temperature dependence of defect signals is shown in Fig. 19(b). No magnetic field direction dependence in signals suggests that defects such as the Pb centers commonly observed at SiO2/Si interface are not located at the GeO2/Ge interface. It was also reported that the Pb centers at the GeO2/Ge interface were not detectable by the conventional ESR.48) This too might be again attributed to more flexible bonds in the Ge–O network, although very small Ge dangling bond signals were later detected using electrically detected magnetic resonance (EDMR) measurement.49)

Download figure:

Standard image High-resolution imageFig. 19. (a) ESR signals inspected at ∼4.5 K from sputtered GeO2/Ge stack before and after annealing in N2, 1 atm O2 and HPO. (b) Spin density (spins/cm3) in GeO2/Ge stack as a function of annealing temperature in N2-PDA. Defect density increases with increasing annealing temperature. No magnetic field dependence was observed, which means that the observed signals are not from the Pb-center-like interface defects.31)

Download figure:

Standard image High-resolution imageX-ray photoelectron spectroscopy (XPS) analysis has been widely used for characterizing SiO2/Si gate stack properties. Although the sub-oxide analysis has not been established in GeO2/Ge yet, most studies employ the same method for GeO2/Ge as that for SiO2/Si by assuming the Ge4+ position at a given binding energy. The value of Ge4+ is substantially scattered among published reports, so it is presently not safe to evaluate the sub-oxide formation kinetics on Ge by using the same XPS analysis used to evaluate them on Si. It is worthwhile mentioning here that the charging effects50) or the moisture effects51) in the XPS measurement of GeO2 should be much more carefully considered than in the XPS measurement of SiO2/Si. HPO-GeO2 is more robust against the charging in XPS measurement (data not shown).

We systematically measured the band offset at GeO2/Ge by both XPS and internal photoemission (IPE) spectroscopy. The IPE study was carried out in Au (∼15 nm)/GeO2/Ge metal–inulator–semiconductor (MIS) capacitors. IPE can determine the conduction band offset at the oxide/semiconductor interface directly.52) Figure 20 shows our IPE system.53) As shown schematically in Fig. 21, the conduction band offset in HPO-GeO2/Ge was estimated to be 1.65 ± 0.1 eV.54) Furthermore, we observed an appreciable spectrum difference between HPO-GeO2/Ge and APO-GeO2/Ge. In APO-GeO2, there seems to be tailing near the photoemission threshold. This suggests that APO-grown GeO2 may have a huge amount of defect states near the conduction band edge. Smaller values of the energy band gap of GeO2 and band offset at GeO2/Ge reported in the literature might be mainly due to poor GeO2 quality.

Fig. 20. Schematic of the internal photoemission measurement system. The sample was irradiated with a fixed number of photons at each wavelength ranging from 320 to 800 nm.53)

Download figure:

Standard image High-resolution imageFig. 21. Band diagram of HPO-GeO2/Ge stack estimated from IPE and XPS results. The energy band gap and band offset at GeO2/Ge are about 6 and 1.6 eV, respectively, which are significantly higher than reported. This is because the band tailing states at the interface are efficiently eliminated by the HPO process.54) It can be seen clearly in Fig. 18.

Download figure:

Standard image High-resolution imageAll of the results obtained experimentally show that HPO can produce high-quality GeO2 on Ge in addition to a considerably low Dit. Thus, it is concluded that HPO and HPO+LOA are powerful methods for preparing perfect GeO2/Ge gate stacks without degrading the quality of the GeO2 bulk film or the GeO2/Ge interface. Moreover, it should be emphasized that everything is thermodynamically controlled in the present process.

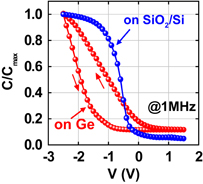

2.3. Kinetic approach

GeO2/Ge interface formation is always associated with GeO desorption, so HPO is thermodynamically effective for making excellent GeO2/Ge gate stacks. On the other hand, we know that actual reactions are often dominated by kinetics rather than thermodynamics. Therefore, a kinetic suppression of GeO desorption from Ge gate stacks has also been attempted. First, the reaction blocking layer was inserted between GeO2 and Ge. 10-nm-thick GeO2 films were deposited on both Ge and SiO2/Si. Figure 22 shows that the C–V characteristics of a Au/GeO2/Ge MOS capacitor are significantly degraded, while those of a Au/GeO2/SiO2/Si MOS capacitor are apparently normal.22) This suggests that excellent gate stacks on Ge can be obtained by putting a more stable interlayer between Ge and GeO2. If so, GeO2 is no longer needed. In that sense, SiO2/Ge gate stacks might be good.

Fig. 22. Bidirectional normalized C–V characteristics of Au/sputtered-GeO2/Ge and Au/sputtered-GeO2/SiO2/Si MIS capacitors in N2-PDA at 600 °C, measured at 1 MHz. GeO2 and SiO2 thicknesses were 10 and 5 nm, respectively. Although the hysteresis observed in the GeO2/Ge stack is scattered from sample to sample, N2-PDA does not degrade gate stacks as long as GeO2 is not in contact with Ge.22)

Download figure:

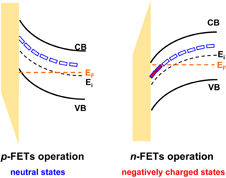

Standard image High-resolution imageIn fact, a number of efforts using Si-cap technology on Ge have been carried out to achieve good performance of Ge gate stacks, mainly by the IMEC group.55,56) In this method, SiO2/(Si)/Ge is used in place of GeO2/Ge gate stacks. As shown in Fig. 23, Si can be expitaxially grown on Ge in a controlled manner by using a continuous growth process in a chamber,57) although the ultimate control of Si thickness and/or Si oxidation is needed to obtain well-controlled gate stacks. This method has been successfully utilized for Ge MOSFETs57,58) and has made it possible to make use of Si process technology without considering how to suppress the reaction at oxides/Ge. It is a great benefit in the Si cap process on Ge. In our experiments, however, Si passivation works well for Dit in the lower half of Eg but degrades the upper half. This means that it may work for p-MOSFETs but not for n-MOSFETs,59) although our passivation was not by the epitaxial Si growth. Furthermore, from the viewpoints that EOT scaling and narrow process window (whether the Si-cap layer is consumed or not is quite marginal even if the cost issue is not taken into account) and poor electron mobility reasons, we have not employed the Si cap process for Ge gate stack formation.

Fig. 23. Cross-sectional TEM images of Si-passivated Ge gate stacks made using various Si deposition times.57) A very thin Si layer epitaxially grown on Ge is observed. Reprinted with permission from Ref. 57. © 2015 IEEE.

Download figure:

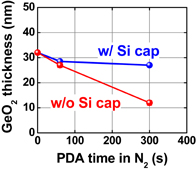

Standard image High-resolution imageAnother kinetic approach is the control by cutting the desorption at the top surface instead of suppressing the reaction at the Ge interface in Eq. (2.1). It is expected that a Si cap might serve as a layer blocking GeO desorption from the top. GeO2 films deposited on Ge with and without a Si cap layer were prepared and then annealed in N2 at 600 °C. Figure 24 shows the annealing time dependence in N2 of GeO2 thickness measured by GIXR. With the Si cap, the thickness changes very little with PDA time, while without the Si cap, it decreases with PDA time.59) This suggests that the Si-capped GeO2/Ge MOS capacitor may reveal a very slight degradation in C–V characteristics. To make the Si-cap conductive as the gate electrode, Ni was deposited, followed by silicidation annealing. Figure 25 shows the C–V characteristics of two kinds of GeO2/Ge gate stacks: a GeO2 MOS capacitor annealed in N2 before Au gate electrode deposition, and a MOS capacitor with NiSix-capped GeO2. Well controlled C–V characteristics were achieved only in the latter case.60) This is direct evidence that the kinetic suppression of GeO desorption significantly improves GeO2/Ge gate stacks.

Fig. 24. Thickness reduction of GeO2 film with and without 10-nm-thick Si cap layer on GeO2 in N2-PDA at 600 °C. The Si cap layer can substantially suppress GeO desorption.59)

Download figure:

Standard image High-resolution imageFig. 25. Bidirectional normalized C–V characteristics of NiSi/GeO2/p-Ge annealed during FUSI gate electrode formation and Au/GeO2/p-Ge annealed before Au deposition. PDA was carried out in N2 for 30 s. In case of FUSI/GeO2, the C–V curve is significantly improved with a small hysteresis, thanks to the suppression of GeO desorption by FUSI capping.60)

Download figure:

Standard image High-resolution imageAlthough we tried to push the kinetic approach forward at the early stage of our Ge research, we have put emphasis on the thermodynamic approach because the metal capping process would be expected to increase the process complexity in device integration. In the material approach discussed in the next section, both the thermodynamic and kinetic approaches are in principle working together. This is a key concept in the EOT scaling discussed in Sect. 4.3.

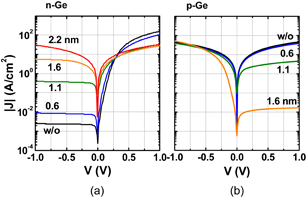

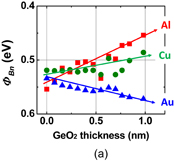

2.4. Materials approach

From the early stage of our Ge research, we have tried to prepare Ge gate stacks with various high-k dielectrics.61) Our experiences gave us the naïve impression then that trivalent metal oxides such as Y2O3, Sc2O3, and Al2O3 or rare-earth oxides (RE-oxides) might be friendly to Ge in terms of the interface control, while HfO2 should significantly degrade the Ge interface. The results of theoretical calculations also gave us that impression.62)

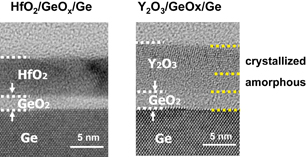

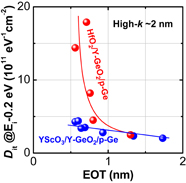

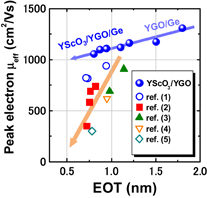

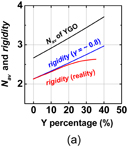

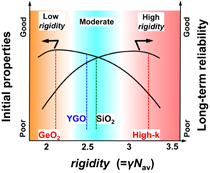

A difference between Y2O3/Ge and HfO2/Ge is seen in the C–V characteristics in Fig. 26(a).59) More distinctly, the interface quality difference is shown in the Zerbst plot63) in Fig. 26(b). Y2O3 on Ge is much better than HfO2 on Ge from the interface control viewpoint. Figure 27 shows that Y2O3/GeO2 is significantly different from HfO2/SiO2 from the viewpoint of intermixing at the interface.59) In fact, as described later in Sect. 3.1, we achieved the highest electron mobility in Ge MOSFETs with a Y2O3-doped GeO2 (YGO) interface formed by HPO-PDA of Y2O3.58,64) Since Y2O3 or Sc2O3 shows the lowest standard Gibbs free energy change (ΔG°) among various oxides thermodynamically, Y or Sc diffusion to GeO2 enables the GeO desorption to be suppressed very effectively. This is discussed in more detail in Sects. 4.2 and 5.2 from the viewpoints of both oxygen potential control and gate stack reliability. Thus, in our experience, we have come to the conclusion that YGO should be a most promising gate dielectric film on Ge. In terms of the EOT scalability, however, YGO can be the interlayer between a real high-k material and Ge because the dielectric constant of YGO is not so high (k = 6–8). This is discussed in Sect. 4.2.

Download figure:

Standard image High-resolution imageFig. 26. (a) Bidirectional C–V characteristics of Au/Y2O3/p-Ge and Au/HfO2/p-Ge capacitors annealed at 400 and 600 °C in N2 for 30 s. (b) Zerbst plots for Au/HfO2/p-Ge and Au/Y2O3/p-Ge MIS capacitors annealed at 600 °C in N2, deduced from the transient capacitance measurements with Vg = 2 V at 120 K. The Y2O3/Ge interface is much better than the HfO2/Ge one in terms of the minority carrier generation time.59)

Download figure:

Standard image High-resolution imageFig. 27. Cross-sectional TEM images of HfO2/GeO2/Ge and Y2O3/GeO2/Ge stacks after annealing at 600 °C in N2. The bottom part of Y2O3 is not crystallized, while all parts of HfO2 are crystallized. Y2O3 is more easily mixed with GeO2 than HfO2.59)

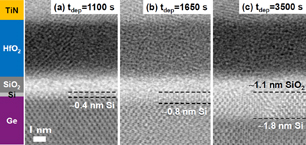

Download figure:

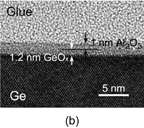

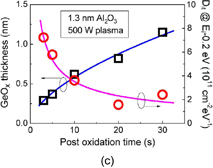

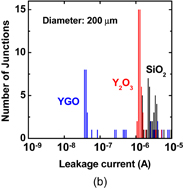

Standard image High-resolution imageIt is practically feasible to use Al2O3 for Ge gate stacks. The Al2O3/GeOx/Ge gate stacks have been intensively studied.65,66) In this process, atomic layer deposition (ALD)-Al2O3 was deposited and the deposition was followed by plasma-excited O* PDA at 300 °C. In fact, Al2O3 is most easily deposited by ALD. The cross-sectional view and TEM image are shown in Figs. 28(a) and 28(b), respectively.66) Takagi's group further reported that the interface GeOx formation was needed to keep the low Dit shown in Fig. 28(c).65) 1-nm-thick GeOx is needed to achieve a low Dit, and the interface is degraded when the thickness is about 0.5-nm-thick GeOx. A good point of this process is that the Al2O3 layer works as a plasma-protection barrier and an oxygen-diffusion stopper in addition to being friendly to the conventional CMOS process.

Download figure:

Standard image High-resolution imageDownload figure:

Standard image High-resolution imageFig. 28. Al2O3/GeOx/Ge gate stacks proposed by Takagi's group. (a) Schematic image of fabricated Ge MOSFET. (b) Cross-sectional TEM image of Al2O3/GeOx/Ge gate stack. (c) GeOx interface layer thickness formed by the ECR plasma post oxidation through 1.3-nm-thick Al2O3 and Dit of Au/Al2O3/GeOx/Ge MOS capacitor as a function of the post oxidation time. Below 1-nm-thick GeOx, Dit increases significantly.66) Reprinted with permission from Ref. 66. © 2012 IEEE.

Download figure:

Standard image High-resolution imageSince we think that Al-strengthened GeO2 might be formed at the interface, it is in some sense similar to the YGO interface proposed above. Namely, both YGO and Al2O3-doped GeO2 can serve as an oxygen-diffusion-blocking layer and stabilize GeO2 by forming the film with modified continuous random network. This is the kinetic control of Ge gate stacks. From this viewpoint, the material approach of selecting the right material requires consideration of the thermodynamic as well as kinetic control of GeO2 on Ge. Both of them are crucially important for establishing reliable ultrathin-EOT gate stacks and so are discussed in Sect. 5.2.

Another material approach is from the rare earth oxides on Ge. Figure 29(a) shows C–V characteristics of a Ge MOS capacitor prepared by HPO of (La–Lu)2O3 (LLO). They look almost ideal.67) It is interesting to note that LLO is a real high-k material (k ∼ 20) and stays amorphous up to around 1000 °C.68) As shown by the TEM image in Fig. 29(b), a rather thick interface layer was formed by HPO. We noted that the interface layer was not pure GeO2 but LLO-mixed GeO2.69) Since we have not optimized the LLO gate stack, we will no longer talk about it in this paper. However, further optimization might make it a great gate stack on Ge.

Download figure:

Standard image High-resolution imageFig. 29. (a) Bidirectional C–V characteristics of (La–Lu)2O3/Ge annealed in HPO at 600 °C. The ratio of La to Lu is ∼1 in this case. (b) Cross-sectional TEM image of HPO (La–Lu)2O3/Ge stack. The C–V curve looks ideal, while a thick amorphous interface layer is grown between (La–Lu)2O3 and the Ge substrate.67)

Download figure:

Standard image High-resolution imageAt the early stage of considering Ge compounds on Ge, GeON instead of pure GeO2 was favorably considered in analogy to SiON in advanced Si technology.70–76) C–V characteristics were much improved, but a high-electron-mobility benefit in Ge n-channel FETs has not so far been reported. We paid attention to the fact that N could also lower the oxygen potential thermodynamically as discussed later in Sect. 3.3.77,78) So GeO desorption could be reduced and the interface properties might be improved by fine-tuning the N profile in GeO2. As we did not have an appropriate technique for the optimum nitridation of Ge for N not to be located at the interface, we stopped studying the GeON gate stack. But it has a potential for the further improving the interface layer.

2.5. Oxidation kinetics of Ge

Ge oxidation at an optimized temperature is obviously the most popular method to form Ge gate stacks, as it is to form Si gate stacks. To suppress GeO desorption, low-temperature oxidation is thermodynamically favored. Matsubara et al. showed that C–V characteristics with a relatively low Dit could be obtained by just oxidizing Ge at 550 °C.79) Although that seems to be inconsistent with our results, we cannot say that there is no process window for improving gate stack characteristics just by a simple oxidation. Nevertheless, even if there might be such a small process window, GeO2 becomes thermodynamically unstable at rather high temperatures above 600 °C.

Although so far we have mainly discussed GeO desorption from GeO2/Ge gate stacks, we actually need to understand Ge oxidation kinetics. As mentioned previously, the oxidation rate of Ge is described by the linear-parabolic law like that describing the oxidation rate of Si. Although as mentioned in Sect. 2.2.2, Ge oxidation appears so related to the GeO desorption process, it is not obvious whether the Deal–Grove model is or is not valid for Ge. Two experimental results that cannot be easily explained by the Deal–Grove model are discussed in the following.

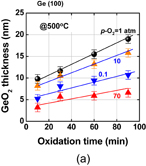

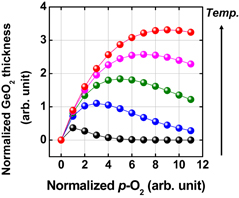

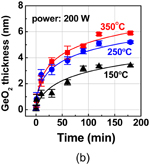

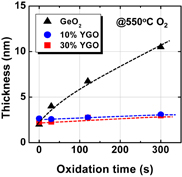

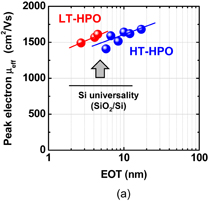

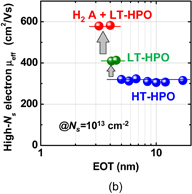

First, the anomalous p-O2 dependence of the rate of Ge oxidation is discussed. Ge(100) wafers were oxidized in wide ranges of temperature and p-O2. GeO2 thickness versus oxidation time at 500 °C is shown in Fig. 30(a) with of p-O2 as a parameter. GeO2 thickness versus p-O2 temperature is shown in Fig. 30(b) with the oxidation temperature as a parameter.80) Note a reverse p-O2 dependence of the oxidation rate. It is surprising that the oxidation rate is reduced below 520 °C as the p-O2 increases above a critical p-O2. This has never been observed in the oxidation of Si. It is hereafter called low-temperature high-pressure O2 (LT-HPO) oxidation. It is strange because a higher p-O2 means a larger amount of O2 molecules in the ambient. Note that in Fig. 30 p-O2 is denoted by the room-temperature p-O2. Anomalous p-O2 dependence in low p-O2 was also discussed in Ref. 21. Therefore, it is general behavior in Ge oxidation, depending on the temperature. Figure 31 shows that (a) the density of LT-HPO GeO2, estimated by GIXR, is greater than that of HT-HPO GeO2 and (b) the wet etching rate is significantly reduced in LT-HPO. This suggests that the reverse p-O2 dependence may be partly due to the densification of the GeO2 film. We applied the Deal–Grove model to characterize the results. To qualitatively reproduce the experimental behavior shown in Fig. 30, improbably large pressure–dependent B parameter in the Deal–Grove equation is needed as shown in Fig. 32.

Download figure:

Standard image High-resolution imageFig. 30. (a) Oxidation time dependence of GeO2 thickness on Ge(100) at 500 °C at various p-O2 values. (b) GeO2 thickness vs p-O2 relationship at various oxidation temperatures, where oxidation time was fixed for 30 min. A reverse p-O2 dependence of the oxidation rate below 520 °C appears around atmospheric p-O2.80) Such characteristics have never been observed in Si oxidation, to the best of our knowledge. Note that, here, p-O2 is the O2 pressure at room temperature before increasing the temperature.

Download figure:

Standard image High-resolution imageDownload figure:

Standard image High-resolution imageFig. 31. (a) Density of GeO2 films grown at 500 and 550 °C as a function of p-O2 estimated by GIXR. It increases with increasing p-O2. (b) Thicknesses of LT-HPO- and APO-grown GeO2 films as a function of wet etching time. Thickness was estimated by XPS. The wet etchant was methanol-diluted water (methanol 100 cm3, H2O 5 cm3). The LT-HPO-grown GeO2 exhibits denser characteristics than the APO-grown one.80)

Download figure:

Standard image High-resolution imageFig. 32. Calculated relationship between GeO2 thickness and p-O2 with normalized oxidation temperature as a parameter. This was calculated using a simple oxidation model with a large pressure–dependent B parameter in the Deal–Grove linear parabolic law.80)

Download figure:

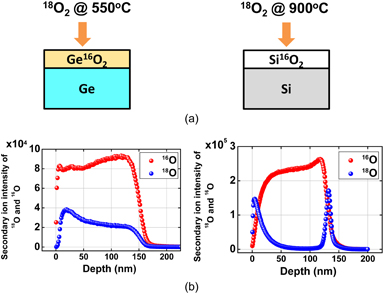

Standard image High-resolution imageTo understand the Ge oxidation correctly, the oxygen atom kinetics should be clarified, since we know that the oxygen atoms diffuse much more easily than Ge in GeO2, as discussed in Fig. 8. In order to trace the oxygen atom movement in the oxidation, the isotope 18O marker experiment was carried out. A Ge16O2 (∼10 nm)/Ge sample grown conventionally was reoxidized by 18O2, and then both 18O and 16O profiles in the film were inspected by the high-resolution Rutherford backscattering spectrometry. The results showed that 18O was not localized at the GeO2/Ge interface but spread throughout the film.81) This is in contrast with the Deal–Grove model commonly recognized for Si. In order to more clearly confirm the oxidation kinetics of Ge, both Ge16O2/Ge and Si16O2/Si samples have recently been prepared again by the normal 16O2 oxidation of Ge and Si substrates, at 550 °C for GeO2/Ge and at 900 °C for SiO2/Si (the temperatures are equivalent to each other when normalized by the melting temperature). The initial thickness was relatively thick (∼120 nm) for both GeO2 and SiO2. Then both were put into a 100% (actually above 98%) 1 atm 18O2 ambient, as shown in Fig. 33(a). The oxide thickness was increased to about 130 nm for both cases. These samples were inspected by the SIMS measurement. The depth profiles of secondary ion intensity of both 18O and 16O are shown for GeO2/Ge and SiO2/Si systems in Fig. 33(b).82) Look at the profile difference of 18O at the Ge interface from that at the Si one. 18O is accumulated at the interface in the Si case, which was as reported previously,83) while in the GeO2/Ge case, 18O gradually decreases to the interface. Since the Deal–Grove model predicts that the oxide is newly formed through the reaction of O2 with semiconductors at the interface, 18O accumulation should be observed as in the Si case. The fact that no special feature at the interface was observed definitely indicates that the Deal–Grove model is not applicable to Ge oxidation.

Fig. 33. (a) Schematic images of samples to trace the 18O atom movement in oxidation process at 550 and at 900 °C in Ge and Si, respectively. (b) Depth profile measured by SIMS of 18O/(18O + 16O) in Si16O2/Si and Ge16O2/Ge stacks after additional 18O2 oxidation. In case of Si, 18O is predominantly detected close to the surface and at the SiO2/Si interface, whereas in case of GeO2/Ge, it is not observed at the interface but is detected almost uniformly (gradually decreasing toward the interface) in the film. This result indicates that Ge oxidation cannot be described by the simple Deal–Grove model.82)

Download figure:

Standard image High-resolution imageWhat is the possible kinetics of Ge oxidation over the Deal–Grove model? Although it is still under investigation, our view is roughly described as follows.82) In case of Ge oxidation, we should take account of GeO desorption, in which Vo diffusion is involved. In fact, a work reported in a recent paper found that the oxygen vacancy Vo may be involved in the oxidation process by inspecting the nuclear reaction profiling of 18O.84) The SIMS results in Fig. 33 also suggest that O atoms should diffuse through the GeO2 film. It is unsure whether this is driven by an exchange process like that discussed in GeO desorption in Sect. 2.1, with the help of Vo formation, or by the interstitial-mediated diffusion.85) The Vo-mediated model, however, seems to be reasonable when it is considered that HPO can suppress Vo generation inside the film thermodynamically, resulting in the significant suppression of the oxidation shown in Fig. 30. Namely, the oxidation of Ge is likely to be driven by the Vo generation at the interface in Eq. (2.4), followed by the reaction between Vo and O. The analytical model like the Deal–Grove one is now under way to establish.

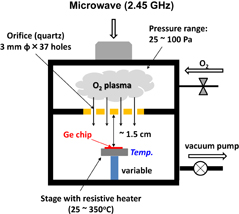

Finally, ozone or O* (oxygen radical) oxidation of Ge is briefly discussed. It was investigated particularly by a group at Stanford University,86) in order to suppress partly GeO desorption by employing a low-temperature process. Ge can be oxidized by ozone or O* at low temperatures with a quite low activation energy, thanks to the high oxidation power of ozone or O*. In the ozone or O* oxidation process, the lifetime of O* concentration, which is dependent on the temperature, should be taken into account. Therefore, the simple Deal–Grove model is not applicable even for the Si case. We studied the O* oxidation of Ge by using O*, which was generated by the µ-wave excited plasma (2.45 GHz) as shown in Fig. 34.87) A distinct difference between normal O2 (including HPO) and O* oxidation is that, as shown in Figs. 35(a) and 35(b), there is little temperature dependence in O* oxidation. C–V characteristics were good, particularly for thin GeO2 formation. However, we stopped the O* process research because the films were not stable at higher temperatures. It may be resumed when the low-temperature oxidation is definitely needed.

Fig. 34. Schematic image of the radical oxidation system used in our experiment. O* was excited by 2.45 GHz microwave. The oxidation space was separated from the O2 plasma space through small quartz orifices.87)

Download figure:

Standard image High-resolution imageDownload figure:

Standard image High-resolution imageFig. 35. Thickness of GeO2 grown by the radical oxidation with the power of (a) 100 and (b) 200 W at various temperatures as a function of oxidation time. Even at low temperatures, Ge was oxidized by O*. The activation energy of O* oxidation was very small (∼0.1 eV).87)

Download figure:

Standard image High-resolution image3. Enhancing electron mobility in Ge MOSFETs

The carrier mobility is one of the most important device properties even in the ballistic transport regime. We, however, will not discuss the Ion/Ioff ratio by fabricating ultra short-channel FETs in this paper. Nevertheless, since the carrier mobility is very sensitive to the interface properties, it is a quality indicator of the carrier transport at the interface. Therefore, intrinsic scattering mechanisms are only discussed in the framework of the Matthiessen's rule. Let us start with the Coulomb scattering discussion first.

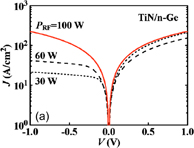

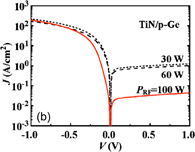

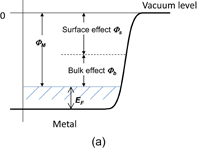

3.1. Dit reduction

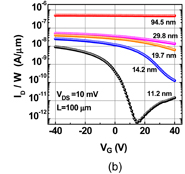

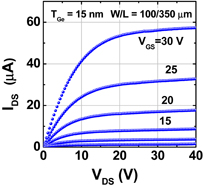

We are interested in Ge CMOS, but as mentioned in the introduction, so far, n-MOSFET technology has actually been a bottleneck. Therefore, it is a big concern that n-channel Ge MOSFETs might be intrinsically poor even though the bulk electron mobility is expected to be high.88) We applied the gate stack formation process described in the previous sections to n-MOSFET fabrication. Long-channel n-MOSFETs were fabricated on a Ge substrate using the two-step HPO+LOA process.38) Several channel lengths (W/L = 90 µm/100–500 µm) were defined, and phosphorus (1 × 1015/cm2 dose) was implanted with 100 keV to form source/drain (S/D) regions. Such large FETs enabled us to estimate electron mobility very accurately using the split C–V technique without being worried about by size uncertainty and/or parasitic resistance and capacitance. GeO2 was grown at 550 °C for 10 min in HPO (p-O2 = 70 atm at room temperature), followed by LOA at 400 °C. Then, Al was deposited and defined for the gate electrode. Note that spacer Y2O3 was used to protect GeO2 from the wet process and air exposure because we found that Y2O3 was water-resistant and rather compatible with Ge as discussed in Sect. 2.4.

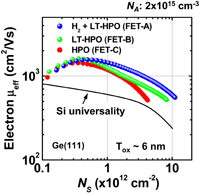

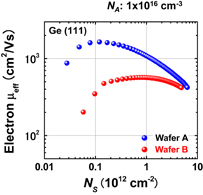

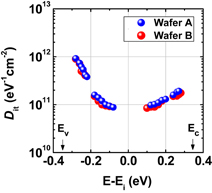

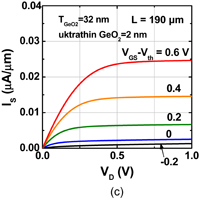

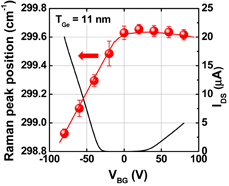

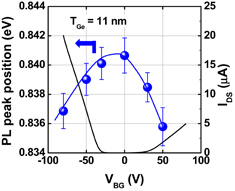

Figure 36(a) shows the transfer characteristics (IS–VG) of Ge(100) n-MOSFETs in which GeO2 was grown by HPO+LOA.38) The Ion/Ioff current ratio at 300 K was about ∼104. The subthreshold swing (S-factor) was 125 mV/dec, which was rather high, considering the low Dit determined using the conductance method (Fig. 14). Since the S-factor should have a linear temperature dependence around room temperature,89) the temperature dependence of the S-factor was measured from 150 to 300 K, as shown in Fig. 36(b). The S-factor at 300 K extrapolated from the temperature dependence was 95 mV/dec,39) which was reasonable and much smaller than the measured value. This suggests that the S-factor at 300 K might be degraded owing to the S/D junction leakage current in the subthreshold region in this device. The impact of LOA on the electron effective mobility (μeff) in addition to that of HPO is shown in Fig. 37 as a function of electron density. On Ge(100), the peak electron mobility after HPO+LOA was 810 cm2 V−1 s−1, while that after HPO was 610 cm2 V−1 s−1. The lower μeff in MOSFET fabricated by HPO only is explainable by the Coulomb scattering due to relatively high values of Dit (Fig. 12).

Download figure:

Standard image High-resolution imageFig. 36. (a) Transfer characteristics of Ge(100) n-MOSFET with a gate stack grown by HPO+LOA at VDS = 5 mV and 1 V. Both ID and IS are shown. (b) Temperature dependence of S-factor (SS) from 150 to 300 K. The S-factor estimated from a linear extrapolation to 300 K is ∼95 mV/dec, which is much smaller than the measured one. This difference may come from the S/D junction leakage current.39)

Download figure:

Standard image High-resolution imageFig. 37. Effective electron mobility as a function of inversion electron density (Ns) in MOSFETs with GeO2 grown both by HPO and HPO+LOA. The peak electron mobility in a GeO2/Ge gate stack grown by HPO+LOA was about 800 cm2 V−1 s−1. By adding LOA, the effective mobility was improved particularly at low electron densities.39) The mobility was estimated by the split C–V method.

Download figure:

Standard image High-resolution image3.2. Substrate surface orientation

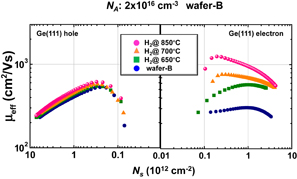

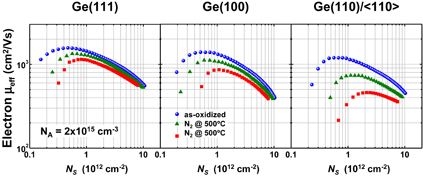

As already mentioned in Sect. 2.2, the surface orientation of Ge substrates affects both the GeO2 formation and GeO desorption processes. In this section, we discuss the effect of substrate surface orientation on electron mobility. Figure 38 shows that the peak electron effective mobility on Ge(111) was about 1,100 cm2 V−1 s−1 at 300 K and was 1.4 times better than that of Ge(100).39) This suggests that the (111) surface should intrinsically be better than the (100) one not only with regard to the process stability as discussed in Sect. 2.2 but also with regard to the FET performance. An advantage of MOSFETs on the Ge(111) surface under the ballistic carrier transport was expected from the analytical estimation of two-dimensional projections in the conduction-band energy.90) The (100) surface in Si, roughly speaking, corresponds to the (111) surface in Ge as shown in Fig. 39. This view is also applicable for the diffusive transport case in terms of the effective mass. In actual scaled CMOS design, the surface orientation effects are discussed in conjunction with strain effects in both Si and Ge.91) In particular, a possible method to make the best of strain effects on the mobility in Fin-FETs is now deliberately studied both experimentally and theoretically,92,93) as obviously expected from two-dimensional projection views. In this review, however, we would focus on unstrained transport characteristics to pay attention to the material and process fundamentals of Ge.

Fig. 38. Substrate orientation dependence of electron mobility in Ge n-MOSFETs with HPO+LOA GeO2 gate stack. The peak electron mobility of 1100 cm2 V−1 s−1 was 1.4 times higher on Ge(111) than that on Ge(100). Note that both values are above the Si universal mobility shown by the solid line. This is the direct observation that Ge(111) has high potential for enhancing the FET performance for the first time.39)

Download figure:

Standard image High-resolution imageFig. 39. Conduction-band energy minima and their projections on (111) and (100) for Ge and Si. Ge(111) is expected to be better than Ge(100) in terms of the lower electron effective mass in the two-dimensional inversion layer. This is in contrast to the Si case.

Download figure:

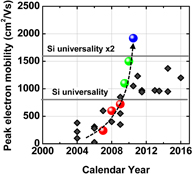

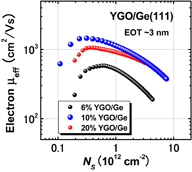

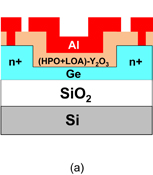

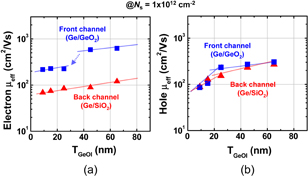

Standard image High-resolution imageWe further improved the electron μeff by optimizing the two-step HPO+LOA process for Y2O3 on Ge(111). Figure 40 shows the peak electron mobility progress with the calendar year.31) The peak electron and hole mobility values obtained so far have approached 1,920 cm2 V−1 s−1 on Ge(111) and 720 cm2 V−1 s−1 on Ge(100). The highest electron mobility case is for Y2O3 on Ge(111) by using the HPO+LOA process with a longer LOA time. It is about ×2.5 of the universal electron mobility in Si MOSFETs and about half of the bulk electron mobility in Ge. Note that, as discussed in Sect. 2.4, the interface of this gate stack is YGO rather than Y2O3. This interface may further decrease Dit, resulting in the peak electron mobility enhancement. Concerning the hole mobility, we have also improved it to ×3.5 that of Si without any strain effect. These results certainly encourage us to promote Ge CMOS. Figure 41 shows the μeff values of electron and hole as functions of electron and hole densities, with different LOA times and different surface orientations of Ge.64)

Fig. 40. Peak electron mobility progress in planar Ge n-MOSFETs with the calendar year. Mobility values reported in the literature are shown by gray diamonds, while our data are shown by colored solid circles.31) The present peak electron mobility in Ge n-MOSFET is higher than twofold the Si one.

Download figure:

Standard image High-resolution imageFig. 41. Effective hole and electron mobilities in Ge p- and n-MOSFETs as a function of carrier density. The highest hole mobility of 725 cm2 V−1 s−1 is roughly 3.5 times higher than Si universal one, and the highest electron mobility of 1920 cm2 V−1 s−1 is a record-high value in Ge n-MOSFETs. With an increase in LOA time, the peak electron mobility is improved.64)

Download figure:

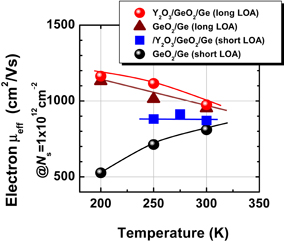

Standard image High-resolution imageIn the conventional mobility analysis, the temperature dependence is the property best characterizing the scattering mechanism in the channel.94) The temperature dependence of the peak electron μeff is shown in Fig. 42, where the slope of temperature dependence changes from positive to negative with an increase in the peak electron μeff. This clearly suggests that the scattering mechanism changes from Coulomb to phonon scattering. Namely, the electron transport in the inversion channel has become intrinsic with dramatic interface improvements. To our knowledge, this is the first demonstration of phonon scattering limited mobility in Ge n-MOSFETs.

Fig. 42. Temperature dependence of electron mobility at Ns = 1 × 1012/cm2. The increase in electron mobility with decreasing the measurement temperature indicates that phonon scattering dominates the electron mobility in the best case with the long LOA time, while the Coulomb scattering degrades the electron mobility with the short LOA time. The importance of LOA should be emphasized from the viewpoint of suppressing the Coulomb scattering.64)

Download figure:

Standard image High-resolution imageEverything so far seems to be good. What is the remaining problem? Concerning the carrier mobility, it has often been claimed that the most relevant mobility in the actual circuit operation is not the peak mobility but that in the high-electron-density region. That is absolutely true. The electron mobility in high Ns region in Fig. 41 is almost comparable to that of the Si counterpart. Does this mean that there is no future for Ge CMOS? In the next section, we focus on this. Another concern is the mobility reduction in the thin EOT region.55) This is actually very important in CMOS scaling and will be discussed in Sect. 4.

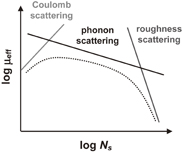

3.3. Atomically flat Ge surface

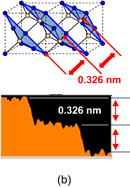

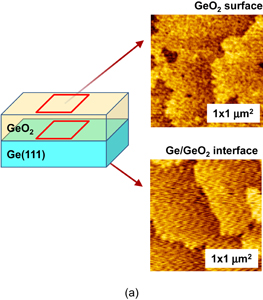

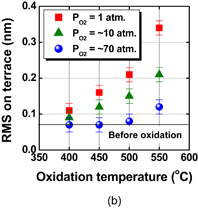

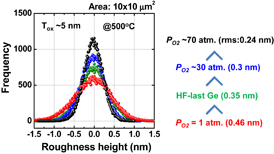

As shown schematically in Fig. 43, Coulomb scattering, phonon scattering, and surface roughness scattering are widely recognized as dominant carrier scattering mechanisms in the Si inversion channel.91) By employing HPO in the Ge oxidation, Coulomb scattering has been dramatically reduced, thanks to the Dit reduction, resulting in the peak electron mobility in Ge now being 2.5 times that in Si. Reasoning by analogy to the Si MOSFET, one may suspect that the larger surface roughness on Ge might degrade the mobility at high electron density (high effective field, Eeff). However, we reported that the rms value measured by the AFM was not necessarily related to the high-Ns electron mobility.95) Here, note that not only the roughness height but also the roughness correlation length should be considered in the conventional roughness scattering formulation.96) We therefore tried to realize the atomically flat surface on Ge in order to achieve both ultimately small rms and large correlation length in the surface roughness.

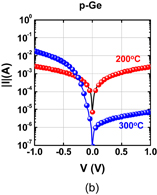

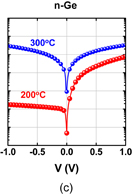

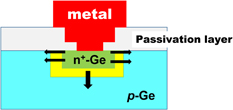

Fig. 43. Schematic of dominant carrier scattering mechanisms in the Si MOS inversion layer. Three mechanisms such as Coulomb, phonon, and surface roughness scatterings are generally considered in the carrier transport in Si MOSFETs. By using the Matthiessen's rule, the carrier mobility is described by the broken line.

Download figure: