### **INVITED REVIEW**

# AlGaN/GaN high-electron-mobility transistor technology for high-voltage and low-on-resistance operation

To cite this article: Masaaki Kuzuhara et al 2016 Jpn. J. Appl. Phys. 55 070101

View the article online for updates and enhancements.

### You may also like

Novel current collapse mode induced by source leakage current in AlGaN/GaN high-electron-mobility transistors and its impact

Kunihiro Tsubomi, Masakazu Muraguchi and Tetsuo Endoh

- GaN-based power high-electron-mobility transistors on Si substrates: from materials to devices

Nengtao Wu, Zhiheng Xing, Shanjie Li et al

Coeffect of trapping behaviors on the performance of GaN-based devices

Xingye Zhou, Xin Tan, Yuangang Wang et al

## AlGaN/GaN high-electron-mobility transistor technology for high-voltage and low-on-resistance operation

Masaaki Kuzuhara, Joel T. Asubar, and Hirokuni Tokuda

Graduate School of Engineering, University of Fukui, Fukui 910-8507, Japan

Received October 27, 2015; accepted April 19, 2016; published online June 10, 2016

In this paper, we give an overview of the recent progress in GaN-based high-electron-mobility transistors (HEMTs) developed for mainstream acceptance in the power electronics field. The comprehensive investigation of AlGaN/GaN HEMTs fabricated on a free-standing semi-insulating GaN substrate reveals that an extracted effective lateral breakdown field of approximately 1MV/cm is likely limited by the premature device breakdown originating from the insufficient structural and electrical quality of GaN buffer layers and/or the GaN substrate itself. The effective lateral breakdown field is increased to 2MV/cm by using a highly resistive GaN substrate achieved by heavy Fe doping. Various issues relevant to current collapse are also discussed in the latter half of this paper, where a more pronounced reduction in current collapse is achieved by combining two different schemes (i.e., a prepassivation oxygen plasma treatment and a field plate structure) for intensifying the mitigating effect against current collapse. Finally, a novel approach to suppress current collapse is presented by introducing a three-dimensional field plate (3DFP) in AlGaN/GaN HEMTs, and its possibility of realizing true collapse-free operation is described. © 2016 The Japan Society of Applied Physics

#### 1. Introduction

GaN-based high-electron-mobility transistors (HEMTs) have achieved continuous progress with the demonstration of promising low-loss and high-voltage switching capabilities for use in next-generation power electronics circuits. This is primarily due to their outstanding intrinsic material and device properties, such as a wide bandgap of 3.4 eV for stable high-temperature operation, a high breakdown electric field of more than 3 MV/cm for high-voltage operation, and a high electron mobility exceeding 1500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for low on-state resistance. In addition, a large conduction band offset between AlGaN and GaN along with polarization charges at the heterointerface induces high-density two-dimensional electron gas (2DEG) with a high mobility. By taking advantage of the high breakdown electric field of GaN, off-state breakdown voltages of over 1kV have been achieved in GaN-based devices. 1-17) Uemoto et al. reported a high breakdown voltage of 8.3 kV with an AlGaN/GaN HEMT having an AlN passivation fabricated on a sapphire substrate,<sup>4)</sup> and later updated their record value of maximum off-state breakdown voltage to 10.4 kV.<sup>5)</sup>

Despite those promising results on breakdown voltages, the measured lateral breakdown electric field in AlGaN/GaN HEMTs, defined as the measured off-state breakdown voltage divided by the gate-to-drain distance  $(L_{\rm gd})$ , was typically around 1 MV/cm, which is significantly lower than the theoretically predicted value of 3.3 MV/cm. Such unexpectedly lower values in breakdown electric field have been reported with AlGaN/GaN HEMTs fabricated on different substrate materials, such as Si, 9-11,13-15,17,18) sapphire, 2-5) and SiC. 1,8,12,16) So far, no clear explanation has been made regarding the discrepancy between the measured effective lateral breakdown field and the predicted value. This is partly because the quality of the buffer layer, which is inserted primarily to compensate the lattice mismatch between GaN and a foreign substrate material, was not sufficiently optimized for high-voltage operation. Srivastava et al. reported a substantial improvement using a novel local substrate removal technique, in which the Si substrate under the source-to-drain region was selectively removed by inductively coupled plasma (ICP) dry etching. 9,10) The local removal of both Si substrate and related interfacial layers resulted in a high breakdown voltage of 2.2 kV, corresponding to a lateral breakdown field of 1.1 MV/cm. The results strongly suggest the importance of improving the quality of buffer and/or substrate materials to achieve even higher breakdown voltages as well as to improve the effective breakdown electric field in GaN-based electron devices.

Regarding the experimental evaluation of the breakdown electric field, more encouraging results have been reported in GaN p-n diodes<sup>19-24)</sup> and GaN vertical MOSFETs.<sup>25-28)</sup> Kizilyalli et al. extracted a critical electric field of more than 3.5 MV/cm from a vertical p-n diode fabricated on a free-standing GaN substrate.<sup>22)</sup> The use of a high-quality n-type GaN drift layer grown on a low-dislocation-density GaN substrate (10<sup>4</sup>-10<sup>6</sup> cm<sup>-2</sup>) was found essential for achieving better breakdown characteristics. These results on GaN-based vertical power devices suggest that substantial improvements in the breakdown characteristics of lateral HEMTs would be possible by fabricating devices on a semi-insulating free-standing GaN substrate.

In addition to the improvement in breakdown characteristics, the reduction in the on-state resistance  $R_{\rm on}$  is also of special importance for next-generation power applications. Although the access and channel resistances of AlGaN/GaN HEMTs are known to be minimized by the benefit of the high electron mobility of 2DEG, this advantage is guaranteed only under static bias conditions. During drain current transients from off-state (pinch-off region) to on-state (linear region), the on-state resistance is often heavily degraded as compared with its static value. This phenomenon of increased dynamic  $R_{\rm on}$  and the subsequent decreased on-state drain current is referred to as "current collapse" and considered as one of the most serious problems to be solved for practical power switching applications of GaN-based HEMTs.

Historically speaking, similar behaviors of dynamic drain current reduction after high-voltage application were observed in n-channel silicon MOSFETs<sup>29)</sup> and CdSe thin-film transistors (TFTs).<sup>30)</sup> Heavily distorted drain current–voltage (*I–V*) characteristics were also observed in AlGaAs/GaAs HEMTs when they were cooled to cryogenic temperatures.<sup>31–33)</sup> This distortion was found to be a temporary phenomenon and could be recovered by shining light onto the devices, suggesting that the drain current "collapse" was due to the injection of hot electrons and eventual trapping in

the AlGaAs layer.<sup>33,34</sup> Similarly, trapping phenomena, called gate lag<sup>35,36</sup> and drain lag,<sup>37,38</sup> became well known to occur at room temperature in GaAs MESFETs and AlGaAs/GaAs HEMTs, leading to premature power saturation in high-frequency power operation. Asano et al. reported the first application of a field plate to avoid undesirable trapping effects in power GaAs MESFETs and AlGaAs/GaAs HEMTs.<sup>39,40</sup>

With the earlier knowledge of trap-related issues in GaAs-based devices, similar problems occur in GaN-based devices, and to make situations more complicated, GaN has a wider bandgap, which admits a variety of deeper traps with longer associated time constants for carrier emission. Furthermore, the high critical electric field of GaN facilitates device operation up to hundreds of volts, leading to the extreme charge injection and trapping of carriers. These intrinsic properties of GaN may make the trap-related collapse issue more noticeable.

The earliest report of current collapse in AlGaN/GaN-based devices was by Khan et al.,<sup>41)</sup> and attributed the current collapse to the trapping of hot electrons in the AlGaN layer. Subsequent studies identified that trapping in the GaN channel<sup>42)</sup> and hot electron injection into GaN buffer layers<sup>43,44)</sup> were also responsible for the observed current dispersion. Meanwhile, the drain current compression observed for GaN-based HEMTs operated at microwave frequencies was highly dependent on gate voltage, which suggested that carrier trapping likely occurred either in the AlGaN barrier or AlGaN surface.<sup>45)</sup>

To explain the current collapse observed in AlGaN/GaN HEMTs subjected to high drain biases with a pinch-off gate bias, Vetury et al. introduced the "virtual gate" model related to surface trapping on the drain side of the gate edge. 46) This surface trap model is widely supported by a number of experimental observations, in which current collapse is mitigated by proper surface passivation with SiN, 47) SiO<sub>2</sub>, 48) Al<sub>2</sub>O<sub>3</sub>,<sup>49)</sup> MgO,<sup>50)</sup> and AlN.<sup>51)</sup> The charge dynamics of surface states due to the trapping/detrapping of carriers are assumed to directly affect the channel 2DEG density, resulting in the change in the on-state resistance and/or drain current. Additionally, several groups<sup>52–58)</sup> have adopted the field-plate technique to relax the electric field in the gateto-drain region. The weakened driving force for charge injection into trap centers eventually resulted in the mitigation in current collapse. However, no single approach has ever succeeded in the complete suppression of current collapse in power GaN-based HEMTs operated at sufficiently high frequencies and bias voltages.

The first half of this paper is devoted to describing the comprehensive characterization of breakdown voltages measured on a series of AlGaN/GaN HEMTs fabricated on a free-standing semi-insulating GaN substrate. The measured breakdown voltages and the extracted lateral breakdown field are characterized in terms of intrinsic and extrinsic structural parameters of the fabricated devices. The possible mechanisms responsible for parasitic leakages and premature device breakdown will be discussed. The latter half of this paper is intended to describe several approaches developed for suppressing current collapse, including high-pressure water vapor annealing (HPWVA), oxygen plasma treatment, GaN cap, field plate (FP), and multimesa channel (MMC). Furthermore, advanced approaches aiming for a more

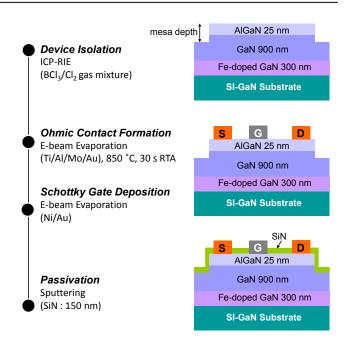

Fig. 1. (Color online) Schematic of fabrication process and subsequent device structure of investigated AlGaN/GaN HEMTs.

pronounced reduction in current collapse are also presented by combining the two schemes mentioned above to enhance the mitigating effect against current collapse. Finally, a novel approach to reduce current collapse is presented by introducing a three-dimensional field plate (3DFP) in AlGaN/GaN HEMTs, and its possibility of realizing true collapse-free operation is discussed.

### 2. Breakdown voltages in AlGaN/GaN HEMTs

### 2.1 Device structure and fabrication

The AlGaN/GaN heterostructures were grown by metalorganic chemical vapor deposition (MOCVD) on 2-in. freestanding GaN substrates. The GaN substrate, prepared by hydride vapor phase epitaxy (HVPE), was doped with Fe with a doping concentration of about  $1\times10^{18}\,\mathrm{cm}^{-3}$  to ensure a semi-insulating property. The threading dislocation density of the starting GaN substrate was nominally  $10^6\,\mathrm{cm}^{-2}$ . The epitaxial structure consists of a 25-nm-thick AlGaN barrier layer, a 900-nm-thick undoped GaN channel layer, and a 300-nm-thick Fe-doped GaN buffer layer. The Al content in the AlGaN barrier layer was 0.2.

Figure 1 shows the simplified schematic of the fabrication process and subsequent device structure. The device fabrication started with mesa isolation using BCl<sub>3</sub>/Cl<sub>2</sub>-based ICP reactive ion etching (RIE). To study the effect of mesa isolation on breakdown characteristics, the mesa etching depth was varied from 200 to 1400 nm. Then, source and drain ohmic contacts were formed by evaporating Ti/Al/Mo/Au metal stacks, followed by rapid thermal annealing at 850 °C for 30 s in an N<sub>2</sub> atmosphere. Ni/Au was then deposited as Schottky gate electrodes. Finally, the devices were passivated with a 150 nm sputter-deposited SiN film. The gate length  $(L_{\rm g})$ , gate width  $(W_{\rm g})$ , and gate-to-source distance  $(L_{\rm gs})$  were fixed at 3, 100, and 3 µm, respectively, while the gate-todrain distance ( $L_{\rm gd}$ ) was varied from 5 to 200  $\mu m$ . Figure 2 shows schematic diagrams of AlGaN/GaN HEMTs fabricated on a semi-insulating GaN substrate with mesa depths of

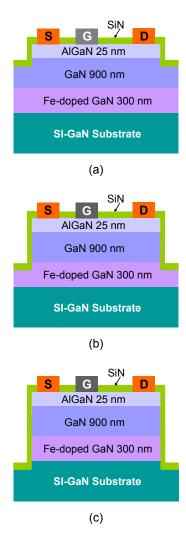

**Fig. 2.** (Color online) Schematic cross-sectional view of AlGaN/GaN HEMTs fabricated on semi-insulating GaN substrate with different mesa depths of (a) 200, (b) 1000, and (b) 1400 nm, where the mesa surfaces fall on undoped GaN channel, Fe-doped GaN buffer layer, and semi-insulating GaN substrate, respectively.

200, 1000, and 1400 nm, where the mesa surfaces are located on the undoped GaN channel, on the Fe-doped GaN buffer layer, and on the semi-insulating GaN substrate, respectively.

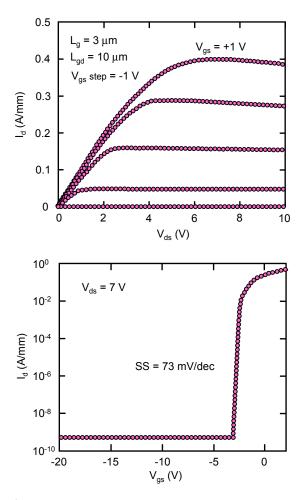

### 2.2 Dependence of breakdown voltage on gate-to-drain distance

Figure 3 shows the output and transfer current–voltage characteristics ( $I_{\rm d}$ – $V_{\rm ds}$  and  $I_{\rm d}$ – $V_{\rm gs}$ ) of the AlGaN/GaN HEMT fabricated on a semi-insulating GaN substrate with a mesa depth of 200 nm and  $L_{\rm gd}=10\,\mu{\rm m}$ . The device exhibited a maximum drain current of 0.4 A/mm, a threshold voltage of –2.9 V, an on-state resistance of  $10\,\Omega$ -mm, an on/off current ratio of  $10^9$ , and a subthreshold swing of  $73\,{\rm mV/dec}$ . Overall DC characteristics were almost the same as those for the HEMT fabricated on a SiC substrate with essentially the same epitaxial structures and device geometry.

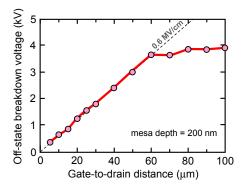

Figure 4 shows the off-state breakdown voltage as a function of  $L_{\rm gd}$  for AlGaN/GaN HEMTs with a mesa depth of 200 nm. The off-state breakdown voltage, defined at a drain current of 1 mA/mm, exhibited a linear increase with the increase in  $L_{\rm gd}$  and reached 3.8 kV at  $L_{\rm gd}$  = 60  $\mu$ m, beyond which the device showed saturation in the breakdown voltage

**Fig. 3.** (Color online) Output and transfer I–V characteristics of AlGaN/GaN HEMT fabricated on semi-insulating GaN substrate with mesa depth of 200 nm and gate-to-drain distance ( $L_{\rm gd}$ ) of  $10\,\mu{\rm m}$ .

Fig. 4. (Color online) Off-state breakdown voltage as function of  $L_{\rm gd}$  for AlGaN/GaN HEMTs with mesa depth of 200 nm.

at approximately 4 kV. From the gradient in the linear region of this plot, the effective breakdown electric field was derived to be 0.6 MV/cm, which is slightly lower than those reported in AlGaN/GaN HEMTs fabricated on foreign substrates such as Si,  $^{9-11,13-15,17,18}$ ) sapphire,  $^{2-5}$ ) and SiC.  $^{1,8,12,16}$ ) Careful observations revealed that catastrophic breakdown was dominant in the linear region up to  $L_{\rm gd}=60\,\mu{\rm m}$ , while the breakdown voltage was determined by the increased leakage current in the saturation region beyond  $L_{\rm gd}=60\,\mu{\rm m}$ . These results suggest the presence of parasitic leakage paths for devices with a mesa depth of 200 nm.

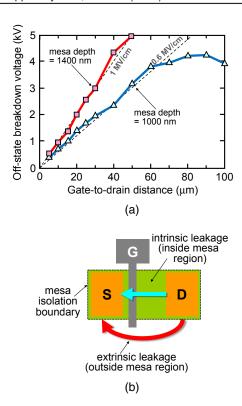

**Fig. 5.** (Color online) (a) Off-state breakdown voltage as a function of  $L_{\rm gd}$  for AlGaN/GaN HEMTs with different mesa depths of 1000 and 1400 nm. (b) Schematic drawing of possible leakage current components under off-state conditions. One is intrinsic leakage current inside mesa region and the other is extrinsic leakage current outside mesa region.

A question therefore arises whether the additional leakage paths originate from the intrinsic (in the mesa isolation region) or extrinsic (outside the mesa isolation region) part of the HEMT device. To address this issue, devices with deeper mesa isolation etching were subjected to similar breakdown voltage measurements in terms of  $L_{\rm gd}$ . Figure 5(a) shows the off-state breakdown voltage as a function of  $L_{\rm ed}$  for AlGaN/ GaN HEMTs with mesa depths of 1000 and 1400 nm. For devices with a mesa depth of 1000 nm, where the surface of mesa isolation is located on the Fe-doped GaN buffer layer, the off-state breakdown voltage was linearly increased up to  $L_{\rm ed} = 60 \, \mu \rm m$  and then became saturated at approximately 4 kV. The total breakdown behavior for the mesa depth of 1000 nm was essentially the same as that for the mesa depth of 200 nm, indicating that the presence of a 900 nm GaN channel layer in the mesa area does not induce additional leakage current components. Meanwhile, an entirely different breakdown behavior was observed for the device with a mesa depth of 1400 nm, where the surface of the mesa isolation is located on the semi-insulating GaN substrate. The 1400 nm mesa-etched devices demonstrated an almost linear increase in the breakdown voltage up to a measurement setup limit of 5 kV. From the slope of the dependence, an effective lateral breakdown field of 1 MV/cm was extracted. This increase in the breakdown field is primarily due to the removal of the Fe-doped GaN buffer layer, suggesting that the presence of the GaN buffer layer permits some premature breakdown and/or flow of non-negligible leakage current in the extrinsic part of the device, as illustrated in Fig. 5(b).

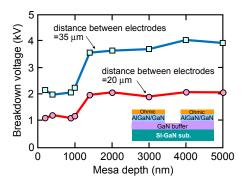

Fig. 6. (Color online) Breakdown voltage as a function of mesa depth for two pairs of ohmic electrodes: one pair separated by  $20\,\mu m$  and the other by  $35\,\mu m$ .

### 2.3 Effect of mesa depth

To understand the effect of mesa etching depth in more detail, two-terminal I-V characteristics were measured between ohmic contact electrodes formed on the same AlGaN/GaN heterostructures. Each ohmic electrode, having a square shape with a width of 100 µm, was mesa isolated by varying the mesa depth from 200 to 5000 nm. Breakdown characteristics were measured between ohmic electrodes separated with distances of 20 and 35 µm as a function of mesa etching depth. As shown in Fig. 6, a steplike increase in breakdown voltage is clearly observed in the mesa depth region between 1000 and 1400 nm. The breakdown voltage became almost constant at mesa depths larger than 1400 nm, where the GaN buffer layer was completely etched away. These results confirm that a higher resistivity in the GaN buffer layer is of substantial importance to achieve better breakdown characteristics in an AlGaN/GaN HEMT structure on a freestanding GaN substrate.

### 2.4 Effect of Fe doping in GaN substrate

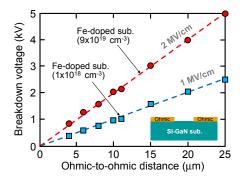

From a series of breakdown measurements for AlGaN/GaN HEMTs fabricated on a semi-insulating GaN substrate with different mesa etching depths, it was found that the highest available breakdown voltage seemed to be restricted by the breakdown and/or the leakage current in a semi-insulating GaN substrate under high applied electric field conditions. To confirm this limitation, the breakdown characteristics were measured between ohmic contact electrodes, which were directly formed on a GaN substrate. Measurements were made on a HVPE-grown free-standing GaN substrate with an Fe doping concentration of  $1 \times 10^{18}$  or  $9 \times 10^{19}$  cm<sup>-3</sup>. Results are shown in Fig. 7, where measured breakdown voltages are plotted as a function of ohmic-to-ohmic distance varied from 4 to 25 µm. For both semi-insulating GaN substrates, the breakdown voltage increased linearly with the increase in the ohmic-to-ohmic distance. Note that an effective lateral breakdown field of as high as 2 MV/cm was achieved for the heavily Fe-doped GaN substrate  $(9 \times 10^{19})$ cm<sup>-3</sup>). This value is, to the best of the authors' knowledge, the highest effective breakdown field ever recorded on the horizontal GaN devices. These results strongly suggest that a higher lateral breakdown field may be achievable by further increasing the resistivity of a semi-insulating GaN substrate through the reduction of the background donor concentration and/or the defect density in a GaN substrate.

**Fig. 7.** (Color online) Breakdown voltage as a function of ohmic-to-ohmic distance of ohmic electrodes formed on top of two types of GaN substrate with different degrees of unintentional carrier compensation: one has an Fe doping concentration of  $1 \times 10^{18} \, \mathrm{cm}^{-3}$  while the other is heavily compensated with  $9 \times 10^{19} \, \mathrm{cm}^{-3}$  Fe doping concentration.

One might think that SiC or sapphire would be more preferable as a starting substrate to achieve higher values in the effective lateral breakdown field in AlGaN/GaN HEMTs because the material has more perfect semi-insulating properties. However, this is not true because more complicated and thicker buffer layers are usually necessary to grow high-quality GaN-based heterostructures. Only a free-standing GaN substrate can permit the growth of very thin buffer GaN layers with controlled high-resistivity properties, which are of particular importance to suppress parasitic leakage current and/or premature breakdown.

### 3. Suppression of current collapse in AlGaN/GaN ${\sf HEMTs}$

### 3.1 Device fabrication

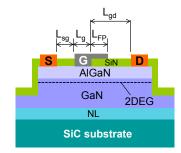

Current collapse is another major hurdle that needs to be properly addressed before the wide-scale adoption of AlGaN/GaN HEMTs for power electronics. This section is devoted to summarizing our recent efforts in exploring alternative solutions towards the suppression of current collapse, such as high-pressure water vapor annealing (HPWVA), oxygen (O2) plasma treatment, introduction of FP, and using 3DFP structures. For gauging the effectiveness of these different approaches to current collapse, the performance of each prototype device employing the above-mentioned schemes was compared with that of a reference device fabricated on the same substrate. This is to avoid processspecific variations in contact resistances and other relevant device parameters that may mask the effect of the different approaches on device performance being measured. Reference devices were fabricated using the same process shown in Fig. 1. For each prototype device employing one of the above-mentioned schemes, additional steps were inserted into the fabrication process, as will be discussed later accordingly. For the purpose of current collapse evaluation, devices were fabricated using an Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN heterostructure grown on a 4H-SiC substrate by MOCVD. The epitaxial structure consists of a 25-nm-thick AlGaN barrier layer, a 500-nmthick undoped GaN channel layer, and an AlN nucleation layer (NL). The AlN NL facilitates high-quality GaN heteroepitaxy by accommodating the lattice mismatch between the GaN layer and the underlying SiC substrate. Unless otherwise specified, for all devices,  $L_{gs}$ ,  $L_{g}$ ,  $L_{gd}$ , and  $W_{g}$  were 3, 3, 10, and 100 μm, respectively.

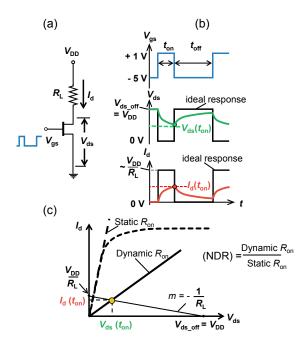

**Fig. 8.** (Color online) Schematic of (a) circuit used for current collapse evaluation showing the drain bias voltage ( $V_{\rm DD}$ ), which provides electrical stress ( $V_{\rm ds.off}$ ) during device off-state, (b) drain current and voltage waveforms, and (c) graphical definition of load lines and dynamic  $R_{\rm on}$ .

### 3.2 Measurement and characterization of current collapse

Figure 8 outlines the important details of the current collapse evaluation method performed on the devices. As given in Fig. 8(a), a drain bias voltage ( $V_{\rm DD}$ ) provided by a power supply (Texio PA600-0.1B) was used in series with a load resistance ( $R_{\rm L}$ ), while a train of gate pulses from a pulse generator (Iwatsu DG 8000) was applied to the gate. The values of  $V_{\rm DD}$  and  $R_{\rm L}$  were appropriately chosen so that the resulting load line intersects the  $I_{\rm d}$ - $V_{\rm ds}$  curve at a point below 1/4 of the maximum drain current. This ensured that  $R_{\rm on}$  being measured was within the linear region. During the offstate,  $V_{\rm DD}$  supplies the offstate drain voltage stress  $V_{\rm ds.off}$ . For mimicking a typical operation under which devices in power switching circuits are subjected, values of the gate voltage ( $V_{\rm gs}$ ) alternating between -5 V (off-state) and +1 V (on-state) were applied to the gate terminal as shown in Fig. 8(b).

For brevity, we first define  $t_{on}$  as a preselected fixed time interval following the rising edge of the gate pulse, during which the device is in the "on" state as illustrated in Fig. 8(b). In other words,  $t_{on}$  is the elapsed time after switching the device from off- to on-state. After every  $t_{on}$ , the corresponding  $V_{ds}(t_{on})$  and  $I_{d}(t_{on})$  were recorded using an oscilloscope (LeCroy WaveRunner 204Xi-A) and used to compute the dynamic  $R_{\rm on}$  as illustrated in Fig. 8(c). For representing current collapse quantitatively, we used the normalized dynamic  $R_{\rm on}$  (NDR), which is defined as the ratio of dynamic  $R_{\text{on}}$  to static  $R_{\text{on}}$ . A higher NDR indicates a higher degree of current collapse. Using the electrical circuit given in Fig. 8(a), we can then monitor how the NDR of the devices evolves with the variation in either  $V_{ds\_off}$  (method 1) or  $t_{on}$  (method 2) for current collapse evaluation. The dependence of NDR on  $t_{on}$  can also be used to estimate the energy levels of the traps responsible for the current collapse as discussed below.

The general expression for  $R_{\text{on}}$  is given by the following relationship:

$$R_{\rm on} = 2R_{\rm c} + R_{\rm s} + R_{\rm ch} + R_{\rm d},\tag{1}$$

where  $R_c$ ,  $R_s$ ,  $R_{ch}$ , and  $R_d$  represent contact resistance, source access resistance, channel resistance, and drain access resistance, respectively. According to the model by Vetury et al.,  $^{46}$  current collapse is due to the trapping of injected electrons on the drain side of the gate edge during the off-state, which eventually depletes the underlying 2DEG in this portion of the gate-to-drain access region, consequently increasing the dynamic  $R_{on}$ , i.e., current collapse. After switching the device from off- to on-state, the drain access resistance transient  $R_d(t)$  can be mathematically given by

$$R_{\rm d}(t) = \frac{1}{e n_{\rm s}(t) \mu} \frac{L_{\rm gd}}{W_{\rm g}},\tag{2}$$

where

$$n_{\rm s}(t) = n_{\rm s}(\infty) - \sum_{i}^{N} \Delta n_{\rm si} \exp\left(-\frac{t}{\tau_i}\right). \tag{3}$$

Here, t is the elapsed time after switching the device from off- to on-state.  $n_s(t)$  and  $n_s(\infty)$  represent the effective drain access region 2DEG density at time t and  $t = \infty$  (static), respectively. As given by Eq. (3), the difference in  $n_s(\infty)$  and  $n_s(t)$  can be given by the sum of pure exponential terms, where  $\Delta n_{si}$  represents the effective sheet density of trapped electrons in the ith trap with a corresponding emission time constant  $\tau_i$  immediately prior to switching the device to the on-state. As t increases, the sum of the exponential terms representing the effective density of trapped electrons approaches zero. Substituting Eq. (3) into Eq. (2) yields

$$R_{\rm d}(t) = \frac{L_{\rm gd}}{W_{\rm g}e\mu} \left[ \frac{1}{n_{\rm s}(\infty) - \sum_{i}^{N} \Delta n_{\rm si} \exp(-t/\tau_i)} \right]. \tag{4}$$

Applying Taylor series approximation on the expression inside the parenthesis, one can easily obtain

$$R_{\rm d}(t) = \frac{L_{\rm gd}}{W_{\rm g}e\mu n_{\rm s}(\infty)} \left[ 1 + \sum_{i}^{N} \frac{\Delta n_{\rm si} \exp(-t/\tau_i)}{n_{\rm s}(\infty)} \right]. \tag{5}$$

Using Eq. (5), we can rewrite Eq. (1) into

$$R_{\rm on}(t) = 2R_{\rm c} + R_{\rm s} + R_{\rm ch} + R_{\rm d}(\infty) \left[ 1 + \sum_{i}^{N} \frac{\Delta n_{\rm si} \exp(-t/\tau_i)}{n_{\rm s}(\infty)} \right], \quad (6)$$

where

$$R_{\rm d}(\infty) = \frac{L_{\rm gd}}{W_{\rm g}e\mu n_{\rm s}(\infty)}. \tag{7}$$

From the definition of NDR, we can finally obtain

NDR

$$\equiv \frac{R_{\text{on}}(t)}{R_{\text{on}}(\infty)} = 1 + \sum_{i}^{N} \alpha_{i} \exp\left(-\frac{t}{\tau_{i}}\right),$$

(8)

where  $\alpha_i$  is the fractional contribution of the *i*th component and is given by

$$\alpha_i = \frac{R_{\rm d}(\infty)}{R_{\rm on}(\infty)} \frac{\Delta n_{\rm si}}{n_{\rm s}(\infty)}.$$

(9)

Note that  $\alpha_i$  is directly proportional to  $\Delta n_{\rm si}$ , which is the effective sheet density of trapped electrons in the *i*th trap immediately prior to switching the device from off- to onstate, and is related to the *i*th trap density itself. In addition, it is worth mentioning that Eq. (8) is very similar in form to the transient drain current expression proposed by Joh and del Alamo.<sup>59)</sup>

The experimentally measured  $t_{\rm on}$  dependence of NDR can be fitted with Eq. (8) to extract the  $\tau_i$  of the *i*th trap level, from which the corresponding ( $E_{\rm C}-E_{\rm t}$ ) energy value can be obtained using the Shockley–Read–Hall (SRH) statistics relationship

$$\tau_i = \frac{1}{v_{\text{th}}\sigma_{\text{n}}N_{\text{C}}} \exp(E_{\text{C}} - E_{\text{t}}). \tag{10}$$

Here,  $v_{th}$  is the electron thermal velocity,  $\sigma_n$  is the capture cross section, and  $N_C$  is the effective density of states at the conduction band edge.

### 3.3 Effect of high-pressure water vapor annealing

There is somewhat a general agreement in the literature that current collapse is predominantly, if not solely, due to trapping on the AlGaN surface. Needless to say, one of the earliest proven approaches against current collapse is AlGaN surface passivation. 47) Because of the high sensitivity of current collapse to AlGaN surface condition, different prepassivation treatment methods should also be explored as alternative solutions. Sameshima and co-workers were the first to demonstrate the applicability of high-pressure water vapor annealing (HPWVA) to semiconductor process technologies. 60,61) They reported improved properties of SiO<sub>2</sub> films and SiO<sub>2</sub>/Si interfaces subjected to HPWVA. It was also found by Punchaipetch et al.<sup>62)</sup> that HPWVA was able to raise the quality of hafnium silicate (HfSi<sub>x</sub>O<sub>y</sub>), which is one of the high- $\kappa$  gate dielectric materials used in modern semiconductor devices. Recently, Yoshitsugu et al. 63) have demonstrated the effectiveness of HPWVA in improving the quality of Al<sub>2</sub>O<sub>3</sub> gate dielectric in n-GaN MOS capacitors. Following these pioneering works, a significant reduction in current collapse was also achieved in AlGaN/GaN HEMTs using HPWVA.64) The HPWVA process was carried out prior to the SiN passivation step. Devices to be subjected to HPWVA were initially set in a sealed chamber. Together with the devices, a predetermined volume of pure water was placed inside the chamber. This volume of water corresponded to the desired pressure at a given setting temperature. A water vapor pressure of 0.5 MPa was used in this work. The chamber was then sealed and heated to a desired annealing temperature for a particular length of time, and then allowed to cool naturally. With a fixed annealing time of 30 min, three different HPWVA conditions corresponding to annealing temperatures of 200, 300, and 400 °C were used.

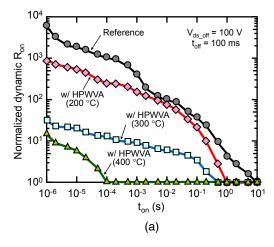

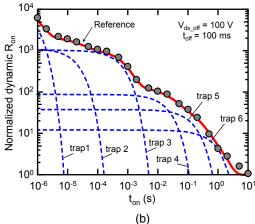

Figure 9(a) shows the measured NDR as a function of  $t_{\rm on}$  of the reference and HPWVA-processed devices. As expected, NDR decreased with increasing  $t_{\rm on}$  for all devices. This is because a longer  $t_{\rm on}$  allowed more time for the emission of trapped electrons, resulting in a greater recovery of dynamic  $R_{\rm on}$ . More importantly, NDR decreased with

**Fig. 9.** (Color online) NDR as a function of on-time ( $t_{\rm on}$ ) of (a) reference and HPWVA-processed AlGaN/GaN HEMTs at fixed drain bias voltage ( $V_{\rm ds.off}$ ) of 100 V and off-time ( $t_{\rm off}$ ) of 100 ms, and (b) reference device with extracted six exponential terms for deep-level traps plotted by dashed curves.

increasing annealing temperature for all HPWVA-processed devices as compared with the reference device, suggesting the efficacy of HPWVA in alleviating current collapse.

By fitting the measured NDR– $t_{\rm on}$  curve with Eq. (8) by the least-squares method, six deep level traps were detected from the reference device, as illustrated in Fig. 9(b). In this figure, extracted exponential terms are plotted by dashed curves, each of which represents a particular trap level. On the other hand, only two levels were detected from the 400 °C HPWVA-processed device. Table I summarizes the extracted values of  $\tau_i$  and  $\alpha_i$  of these trap levels. Assuming  $v_{\rm th}$  of  $2.6 \times 10^7 \, {\rm cm/s}$ ,  $\sigma_{\rm n}$  of  $1.0 \times 10^{-15} \, {\rm cm^2}$ , and  $N_{\rm C}$  of  $2.2 \times 10^{18} \, {\rm cm^{-3}}$ , the trap energy level ( $E_{\rm C} - E_{\rm t}$ ) values given in the fourth column of Table I were obtained using Eq. (10).

The  $(E_{\rm C}-E_{\rm t})$  values ranged from 0.28 to 0.64 eV and from 0.28 to 0.37 eV for the reference and the HPWVA-processed device, respectively. The corresponding  $\alpha_i$  of traps after HPWVA were orders of magnitude lower than those of the reference device. Subsequent X-ray photoelectron spectroscopy (XPS) analyses revealed the chemical blue shift of Ga Auger LMM signals from the HPWVA-processed AlGaN surface relative to those of the reference sample, suggesting the formation of the surface oxide layer of  ${\rm Ga_2O_3}$  and possibly interfacial  ${\rm Ga_2O}$  sub-oxide, which was reported to be essential for achieving low defect density in III–V surfaces. On a final note, HPWVA is considered to

**Table I.** Extracted trap energy levels  $(E_C - E_t)$  from reference (w/o HPWVA) and HPWVA-processed (400 °C) devices.

| Device                   | $\alpha_i$          | $	au_i$ (s)          | $E_{\rm C} - E_{\rm t}$ (eV) |

|--------------------------|---------------------|----------------------|------------------------------|

| Reference<br>(w/o HPWVA) | $1.2 \times 10^{4}$ | $8.0 \times 10^{-7}$ | 0.28                         |

|                          | $1.1 \times 10^{3}$ | $2.4 \times 10^{-5}$ | 0.37                         |

|                          | $1.0 \times 10^{3}$ | $7.1 \times 10^{-4}$ | 0.45                         |

|                          | 88                  | $2.5 \times 10^{-2}$ | 0.54                         |

|                          | 38                  | $1.8 \times 10^{-1}$ | 0.59                         |

|                          | 12                  | $9.0 \times 10^{-1}$ | 0.64                         |

| HPWV-annealed (400 °C)   | 25.9                | $7.4 \times 10^{-7}$ | 0.28                         |

|                          | 7.5                 | $2.5\times10^{-5}$   | 0.37                         |

promote oxygen incorporation, which leads to the formation of surface oxide suitable for device passivation, occupation of near-surface nitrogen vacancies, and termination of unbounded near-surface Ga and Al atoms. <sup>16)</sup> All of these effectively decreased the number of surface states that trap carriers, leading to a highly reduced current collapse.

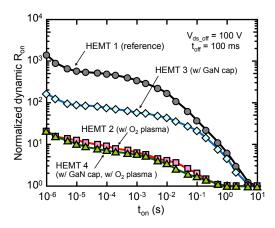

### 3.4 Effect of O<sub>2</sub> plasma treatment and GaN cap

Various gas-plasma treatments of AlGaN surface were reported to be effective in mitigating current collapse.<sup>69–71)</sup> Recently, a significant reduction in current collapse has been demonstrated for O<sub>2</sub> plasma-treated AlGaN/GaN HEMTs as evidenced by highly reduced NDR in these devices over that of a reference device. 72) The AlGaN surface of the devices was exposed to O2 plasma with an RF power of 100 W and an exposure time of 60 s. This was carried out prior to a SiN passivation step of the fabrication process shown in Fig. 1. Meanwhile, there were also reports that an epitaxial GaN cap layer was capable of reducing current collapse. 73-77) Aware of these reports, we also applied O<sub>2</sub> plasma surface treatment to the fabrication of AlGaN/GaN HEMTs having a GaN cap layer. Four different devices with the following features were fabricated: (1) without GaN cap and without O<sub>2</sub> plasma treatment as reference device; (2) without GaN cap and with O<sub>2</sub> plasma treatment; (3) with GaN cap and without O<sub>2</sub> plasma treatment; and (4) with GaN cap and with O<sub>2</sub> plasma treatment. Figure 10 presents the NDR values of the four devices as a function of  $t_{on}$ . Careful investigation of the resulting NDR-ton curves led to the following two important conclusions: (1) O<sub>2</sub> plasma treatment was more effective than the GaN cap in suppressing current collapse and (2) the GaN cap layer approach was redundant and insignificant to current collapse mitigation when used in combination with O<sub>2</sub> plasma treatment. These key findings suggest that by using only O<sub>2</sub> plasma treatment, one can avoid the problems associated with surface GaN layers, such as increased leakage current and difficulty in obtaining good ohmic contacts. 76,77) Following the fitting procedure of NDR-ton curves and analysis using SRH statistics, the characteristic  $\tau_i$ 's and the equivalent energy levels of traps present in each device were extracted. The results, summarized in Table II, suggest that the O<sub>2</sub> plasma treatment is more effective than the GaN cap approach because the O2 plasma treatment leads to a significant reduction in surface trap densities, as suggested by its smaller  $\alpha_i$  values. Moreover, it also completely eliminated two of the deepest trap levels located at  $\sim 0.62$  and  $\sim 0.67$  eV.

**Fig. 10.** (Color online) NDR as a function of on-time ( $t_{\rm on}$ ) of HEMT 1 (reference), HEMT 2 (with  $O_2$  plasma treatment, without GaN cap), HEMT 3 (without  $O_2$  plasma treatment, with GaN cap), and HEMT 4 (with  $O_2$  plasma treatment, with GaN cap) at fixed drain bias voltage ( $V_{\rm DD} = V_{\rm ds.off}$ ) of 100 V and off-time ( $t_{\rm off}$ ) of 100 ms.

**Table II.** Device description and respective extracted trap energy levels  $(E_{\mathbb{C}}-E_{\mathbb{t}})$ .

| Device             | O <sub>2</sub> plasma<br>treatment | GaN cap | $\alpha_i$ | $	au_i$ (s)           | $E_{\rm C} - E_{\rm t}$ (eV) |

|--------------------|------------------------------------|---------|------------|-----------------------|------------------------------|

| HEMT 1 (reference) | NO                                 | NO      | 4968       | $5.66 \times 10^{-7}$ | 0.27                         |

|                    |                                    |         | 269        | $1.80\times10^{-5}$   | 0.36                         |

|                    |                                    |         | 294        | $2.68\times10^{-3}$   | 0.49                         |

|                    |                                    |         | 142        | $3.95\times10^{-2}$   | 0.56                         |

|                    |                                    |         | 24         | $3.97 \times 10^{-1}$ | 0.62                         |

|                    |                                    |         | 3.6        | $2.72 \times 10^{0}$  | 0.67                         |

| НЕМТ 2             | YES                                | NO      | 20         | $8.31 \times 10^{-7}$ | 0.28                         |

|                    |                                    |         | 6.2        | $3.89\times10^{-5}$   | 0.38                         |

|                    |                                    |         | 4.3        | $2.21\times10^{-3}$   | 0.48                         |

|                    |                                    |         | 3.0        | $1.03\times10^{-1}$   | 0.58                         |

| НЕМТ 3             | NO                                 | YES     | 178        | $8.31 \times 10^{-7}$ | 0.28                         |

|                    |                                    |         | 32         | $3.89\times10^{-5}$   | 0.38                         |

|                    |                                    |         | 27         | $5.77 \times 10^{-3}$ | 0.51                         |

|                    |                                    |         | 30         | $8.53 \times 10^{-2}$ | 0.58                         |

|                    |                                    |         | 12         | $5.83\times10^{-1}$   | 0.63                         |

| НЕМТ 4             | YES                                | YES     | 20         | $1.22 \times 10^{-6}$ | 0.29                         |

|                    |                                    |         | 6.0        | $2.18\times10^{-5}$   | 0.36                         |

|                    |                                    |         | 4.0        | $3.93\times10^{-3}$   | 0.50                         |

|                    |                                    |         | 2.3        | $8.53 \times 10^{-2}$ | 0.58                         |

The GaN cap approach, on the other hand, only eliminated the deepest trap level at  ${\sim}0.67\,\text{eV}$ . The more pronounced current collapse suppression in O2-plasma-treated devices, with or without GaN cap, was likely due to the formation of surface oxide, the termination of the near-surface Ga and Al atoms, and the occupation of nitrogen vacancies.  $^{16)}$  These suppositions were supported by data from XPS investigations, which indicated oxygen atom incorporation and the subsequent formation of a 2-nm-thick surface oxide after  $O_2$  plasma exposure.

### 3.5 Effect of field plate

The use of the FP structure in AlGaN/GaN HEMTs dates back from the early 2000s. Ando et al. were the first to demonstrate high-voltage and high-efficiency microwave

**Fig. 11.** (Color online) Schematic cross-sectional view of field-plated AlGaN/GaN HEMT illustrating field plate length ( $L_{\rm FP}$ ) and its relationship with relevant device parameters.

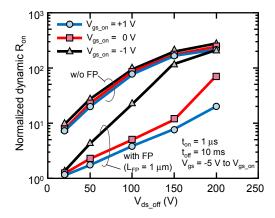

**Fig. 12.** (Color online) NDR as a function of off-state drain bias voltage  $(V_{\text{ds.off}})$  of reference (without FP) and field-plated devices with varying onstate gate voltage  $(V_{\text{gs.on}})$ .

power performance using gate-FP in AlGaN/GaN HEMTs. 52) They already noticed experimentally the importance of gate-FP in reducing current collapse as well as in improving device breakdown characteristics. Using the same FP technology, Okamoto et al. achieved the first over 200 W one-chip microwave power operation at 2 GHz.<sup>53)</sup> Since then, a number of papers have been published reporting that FP in AlGaN/GaN HEMTs is effective in enhancing device breakdown voltages. 54-57) The FP structure redistributes the electric field profile along the drain access region, leading to a reduced electric field peak near the drain side of the gate edge and eventual breakdown voltage enhancement. Therefore, in principle, current collapse, which is considered to be due to trapping on the AlGaN surface of injected electrons from the metal gate, should also be reduced by the introduction of FP. Saito et al. reported improved collapse behaviors of the dual-FP HEMT over the single-FP device and attributed this difference to the leveled electric field distribution in the gate-to-drain region under off-state high-voltage biasing conditions.<sup>55)</sup>

The beneficial FP effects on current collapse were experimentally verified not only during the off-state but also during the on-state in the power switching operation. Hasan et al. fabricated an AlGaN/GaN HEMT with a gate-FP, as illustrated in Fig. 11, and measured the dynamic  $R_{\rm on}$  as a function of on-state  $V_{\rm gs}$  from -1 to +1 V.<sup>58</sup>) As clearly shown in Fig. 12, applying a more positive on-state  $V_{\rm gs}$  resulted in the greater reduction of current collapse for the gate-FP device, but no such gate-bias dependence was observed for the standard HEMT without FP. Note that with decreasing on-state  $V_{\rm gs}$  to -1 V, the NDR of the gate-FP HEMT approaches

that for the HEMT without FP. This result revealed that the gate-FP has an important effect on current collapse during the on-state. Through the field-effect charge control of the gate-FP on channel electrons, the positively biased gate-FP is particularly effective in instantly recovering the partial depletion of channel electrons, which was caused by electron trapping during the off-state. Such beneficial effect during the on-state is peculiar to the gate-FP and would not be expected for the source-FP.

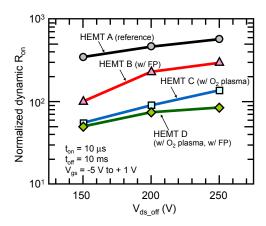

3.6 Combination of O<sub>2</sub> plasma treatment and field plate Aiming for a true "collapse-free" operation, attempts of combining different approaches against current collapse were also reported. It was suggested that using simultaneously two different approaches in mitigating current collapse did not necessarily guarantee a cumulative effect. 72) To put it explicitly, it was found that the GaN cap layer contributed no further reduction in current collapse in the devices already subjected to O<sub>2</sub> plasma treatment. Another report described a systematic investigation of the combined effect of O<sub>2</sub> plasma treatment and FP structure on current collapse. 78) For that purpose, four different devices with the following features were fabricated: (1) reference, (2) with FP, (3) with  $O_2$ plasma treatment, and (4) with FP and with O2 plasma treatment, referred as HEMT A, B, C, and D, respectively. For the O<sub>2</sub>-plasma-treated devices, the AlGaN surface was subjected to O<sub>2</sub> plasma treatment using the same plasma power of 100 W and exposure time of 60 s before SiN passivation. Figure 13 shows NDR as a function of  $V_{ds\_off}$ . As expected, all devices exhibited the increasing trend of current collapse with increasing  $V_{ds\_off}$ . It was found that the  $O_2$ plasma treatment approach led to a stronger degree of current collapse suppression over the FP approach. Interestingly, the device with both FP and O<sub>2</sub> plasma treatment showed the lowest degree of current collapse, indicating the cumulative effect of FP and O2 plasma treatment approaches in weakening current collapse. Asubar et al. explained that the effectiveness of the combined schemes was due to the fact that each scheme dealt with current collapse in a different way. <sup>78)</sup> While O<sub>2</sub> plasma treatment reduced or eliminated

**Fig. 13.** (Color online) NDR as a function of off-state drain bias voltage  $(V_{ds.off})$  of HEMT A (reference), HEMT B (without  $O_2$  plasma treatment, with FP), HEMT C (with  $O_2$  plasma treatment, without FP), and HEMT D (with  $O_2$  plasma treatment, with FP).

surface trap densities responsible for current collapse, the FP structure modified the driving forces directly affecting the trapping and detrapping processes connected with current collapse.<sup>53–56)</sup>

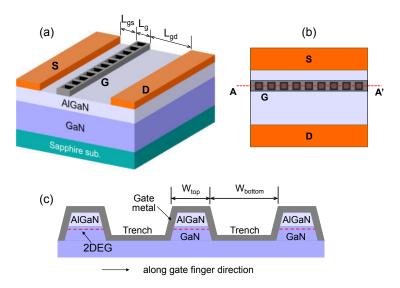

#### 3.7 Multimesa channel

The multimesa-channel (MMC) AlGaN/GaN HEMT, schematically illustrated in Fig. 14, was an interesting structure-based approach of mitigating current collapse. The MMC device was fabricated by etching periodic trenches to form multiple mesas under the metal gate,  $^{79,80}$ ) hence the name multimesa channel. Each mesa channel, formed by electron beam lithography, was designed to have a width ( $W_{\text{top}}$ ) of less than 100 nm. The resulting structure facilitated the modulation of 2DEG not only through the top but also through the sidewalls, improving the device gate control over the drain current. Ohi et al. found that the device was less sensitive to changes in drain access resistance brought about by increasing  $L_{\text{GD}}$  or trapping, and therefore less susceptible to current collapse.  $^{82,83}$ ) They argued that this was due to the much higher resistance of the mesa channel compared with

Fig. 14. (Color online) Schematic illustration of MMC AlGaN/GaN HEMTs: (a) bird's eye view, (b) plan view, and (c) cross-sectional diagram along the cut-plane A-A' shown in (b).

Fig. 15. (Color online) Schematic illustration of 3DFP AlGaN/GaN HEMTs: (a) bird's eye view, (b) plan view, and (c) cross-sectional diagram along the cut-plane A-A' shown in (b).

that of the drain access region. This device, however, had a drawback of decreased net drain current per chip size due to the etching of active sections of the channel to form the trenches.

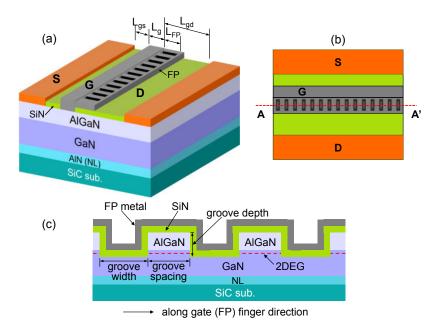

### 3.8 Three-dimensional field plate structure

As discussed in the previous section, field-plate technology is well recognized as a powerful tool to achieve reduced current collapse without inducing any adverse effects in the device DC characteristics. However, a true collapse-free operation has not yet been established. Since the gate-FP in AlGaN/ GaN HEMTs is proven effective to achieve significant current collapse reduction, enhancing the charge-control ability of the gate-FP would help maximize the efficiency of current collapse suppression. Meanwhile, it was verified that the addition of the lateral field effect in the configuration of the multimesa channel was effective in reducing current collapse. However, the removed section in the channel region reduced the effective active device width, leading to the decrease in the total drain current. This means eventual degradation in the on-resistance per chip size, which is of course detrimental for power device applications.

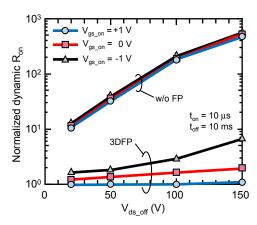

A new type of field plate device was developed with a view of intensifying the current collapse mitigating effect by FP. The structure is schematically illustrated in Fig. 15, in which multiple grooves were selectively fabricated in the field-plate area outside the channel region to avoid the sacrifice in total drain current normally inherent in MMC and trigate devices.<sup>84)</sup> The developed HEMT with 3DFP, also referred to as a multi-grooved field plate (MGFP), exhibited almost collapse-free operation with essentially negligible penalty in the total drain current density. Typical values of groove length, width, depth, and spacing were 2.5, 0.3, 0.2, and 0.9 µm, respectively. Figure 16 compares NDR as a function of  $V_{ds\_off}$  of the reference device (without FP) and the 3DFP HEMT at different values of on-state gate voltage  $(V_{\rm gs\ on})$ . The reference device exhibited almost overlapping NDR- $V_{\rm ds\_off}$  curves with varying  $V_{\rm gs\_on}$ , whereas the 3DFP

**Fig. 16.** (Color online) NDR as a function of off-state drain bias voltage  $(V_{ds.off})$  of reference (without FP) and 3DFP AlGaN/GaN HEMTs with varying on-state gate voltage  $(V_{gs.on})$ .

HEMT showed NDR– $V_{\rm ds.off}$  curves highly sensitive to the applied  $V_{\rm gs.on}$ . For the 3DFP HEMT, at a given  $V_{\rm ds.off}$ , a more positive  $V_{\rm gs.on}$  resulted in a lower NDR, a trend typically observed from gate-FP devices as discussed above. However, this tendency of decreasing NDR, and therefore weakening current collapse with increasing  $V_{\rm gs.on}$ , was clearly more pronounced in the 3DFP HEMT. The resulting side-wall structures confined in the FP area, which allows not only vertical, but also lateral "field-effect action" during the onstate, helped in the faster recovery of trapped electrons responsible for current collapse, thereby intensifying the FP mitigating effect. As shown in Fig. 16, the 3DFP-HEMT exhibited an NDR value of essentially equal to 1 even at  $V_{\rm ds.off}$  of as high as 150 V, suggesting that this device may hold the key toward true "collapse-free" operation.

### 4. Conclusions

With the increasing emphasis for developing highly efficient and "greener" electronic devices, GaN-based electron devices have been generating significant interest in the field of power electronics. In the first half of this paper, after briefly describing the outstanding material properties of GaN and reviewing historical relevant efforts to achieve high breakdown voltages in GaN-based HEMTs, experimental results were presented for pushing the lateral breakdown field toward its theoretical limit. Systematically performed series of experiments on AlGaN/GaN HEMTs, fabricated on a free-standing semi-insulating GaN substrate, identified that parasitic leakage paths responsible for premature device breakdown were likely due to the insufficient structural and electrical quality of GaN buffer layers and the GaN substrate itself. The preparation of a highly resistive semi-insulating GaN substrate, which was realized through carrier compensation by heavy Fe doping  $(9 \times 10^{19} \,\mathrm{cm}^{-3})$ , resulted in an effective lateral breakdown field of 2 MV/cm along with a lateral breakdown voltage of 5 kV. This was the highest lateral breakdown field ever reported from any lateral GaN structures. The second half of the paper was devoted to describing various issues relevant to current collapse in AlGaN/GaN HEMTs. Those included experimental procedures to measure current collapse, derivation of formulae to express normalized dynamic  $R_{\rm on}$  (NDR) as a measure of the degree of current collapse, and various experimental attempts to reduce current collapse. By fitting measured NDR curves with a sum of pure exponential terms, important information on the relevant trap states was extracted. The successful combination of two different schemes for intensifying the mitigation effect against current collapse was demonstrated. Finally, a novel device with a 3DFP was shown to exhibit a negligible increase in the dynamic  $R_{\rm on}$  even after being subjected to an off-state drain voltage of 150 V, suggesting that this device may hold the key for true collapse-free operation.

### Acknowledgements

This work was partially supported by Grant-in-Aid for Scientific Research (C) (No. 25420328) from JSPS and by a Super Cluster Program from JST. This work was also supported by the Council for Science, Technology and Innovation (CSTI), Cross-ministerial Strategic Innovation Promotion Program (SIP), "Next-generation power electronics" (funding agency: NEDO). The authors would like to thank Professor Kazuyuki Tadatomo, Yamaguchi University, for providing highly resistive GaN substrates. Contributions by Yoshiki Sakaida, Jie Hong Ng, Satoshi Yoshida, and Atsuya Suzuki are also appreciated.

- Y. Dora, A. Chakraborthy, L. McCarthy, S. Keller, S. P. DenBaars, and U. K. Mishra, IEEE Electron Device Lett. 27, 713 (2006).

- Y. C. Choi, M. Pophristic, B. Peres, M. G. Spencer, and L. F. Eastman, J. Vac. Sci. Technol. B 24, 2601 (2006).

- N. Tipirneni, A. Koudymov, V. Adivarahan, J. Yang, G. Simin, and M. A. Khan, IEEE Electron Device Lett. 27, 716 (2006).

- 4) Y. Uemoto, D. Shibata, M. Yanagihara, H. Ishida, H. Matsuo, S. Nagai, N. Batta, M. Li, T. Ueda, T. Tanaka, and D. Ueda, IEDM Tech. Dig., 2007, p. 861

- M. Yanagihara, Y. Uemoto, T. Ueda, T. Tanaka, and D. Ueda, Phys. Status Solidi A 206, 1221 (2009).

- K. S. Boutros, S. Burnham, D. Wong, K. Shinohara, B. Hughes, D. Zehnder, and C. McGuire, IEDM Tech. Dig., 2009, p. 161.

- 7) B. Lu and T. Palacios, IEEE Electron Device Lett. 31, 951 (2010).

- E. Bahat-Treidel, F. Brunner, O. Hilt, E. Cho, J. Wurfl, and G. Trankle, IEEE Trans. Electron Devices 57, 3050 (2010).

- 9) P. Srivastava, J. Das, D. Visalli, J. Derluyn, M. Van Hove, P. E.

- Malinowski, D. Marcon, K. Geens, K. Cheng, S. Degroote, M. Leys, M. Germain, S. Decoutere, R. P. Mertens, and G. Borghs, IEEE Electron Device Lett. 31, 851 (2010).

- P. Srivastava, J. Das, D. Visalli, M. Van Hove, P. E. Malinowski, D. Marcon, S. Lenci, K. Geens, K. Cheng, M. Leys, S. Decoutere, R. P. Mertens, and G. Borghs, IEEE Electron Device Lett. 32, 30 (2011).

- J.-G. Lee, B.-R. Park, H.-J. Lee, M. Lee, K.-S. Seo, and H.-Y. Cha, Appl. Phys. Express 5, 066502 (2012).

- 12) H. S. Lee, D. Piedra, M. Sun, X. Gao, S. Guo, and T. Palacios, IEEE Electron Device Lett. 33, 982 (2012).

- D. Christy, T. Egawa, Y. Yano, H. Tokunaga, H. Shimamura, Y. Yamaoka, A. Ubukata, T. Tabuchi, and K. Matsumoto, Appl. Phys. Express 6, 026501 (2013)

- O. Seok, W. Ahn, M.-K. Han, and M.-W. Ha, Electron. Lett. 49, 425 (2013).

- N. Herbecq, I. Roch-Jeune, N. Rolland, D. Visalli, J. Derluyn, S. Degroote,

M. Germain, and F. Medjdoub, Appl. Phys. Express 7, 034103 (2014).

- 16) M. Kuzuhara and H. Tokuda, IEEE Trans. Electron Devices 62, 405 (2015).

- N. Herbecq, I. Roch-Jeune, A. Linge, B. Grimbert, M. Zegaoui, and F. Medjdoub, Electron. Lett. 51, 1532 (2015).

- 18) M. Wang, Y. Wang, C. Zhang, B. Xie, C. Wen, J. Wang, Y. Hao, W. Wu, and K. Chen, IEEE Trans. Electron Devices 61, 2035 (2014).

- Y. Hatakeyama, K. Nomoto, N. Kaneda, T. Kawano, T. Mishima, and T. Nakamura, IEEE Electron Device Lett. 32, 1674 (2011).

- K. Nomoto, Y. Hatakeyama, H. Katayose, N. Kaneda, T. Mishima, and T. Nakamura, Phys. Status Solidi A 208, 1535 (2011).

- Y. Hatakeyama, K. Nomoto, A. Terano, N. Kaneda, T. Tsuchiya, T. Mishima, and T. Nakamura, Jpn. J. Appl. Phys. 52, 028007 (2013).

- I. C. Kizilyalli, A. P. Edwards, H. Nie, D. Disney, and D. Bour, IEEE Trans. Electron Devices 60, 3067 (2013).

- I. C. Kizilyalli, A. P. Edwards, H. Nie, D. Bour, T. Prunty, and D. Disney, IEEE Electron Device Lett. 35, 247 (2014).

- I. C. Kizilyalli, T. Prunty, and O. Aktas, IEEE Electron Device Lett. 36, 1073 (2015).

- H. Otake, K. Chikamatsu, A. Yamaguchi, T. Fujishima, and H. Ohta, Appl. Phys. Express 1, 011105 (2008).

- M. Kodama, M. Sugimoto, E. Hayashi, N. Soejima, O. Ishiguro, M. Kanechika, K. Itoh, H. Ueda, T. Uesugi, and T. Kachi, Appl. Phys. Express 1, 021104 (2008).

- T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, Appl. Phys. Express 7, 021002 (2014).

- T. Oka, T. Ina, Y. Ueno, and J. Nishii, Appl. Phys. Express 8, 054101 (2015).

- 29) T. H. Ning, C. M. Osburn, and H. N. Yu, J. Electron. Mater. 6, 65 (1977).

- 30) F. C. Luo, J. Vac. Sci. Technol. 16, 1045 (1979).

- T. J. Drummond, S. L. Su, W. G. Lyons, R. Fisher, W. Kopp, and H. Morkoc, Electron. Lett. 18, 1057 (1982).

- R. Fischer, T. J. Drummond, W. Kopp, and H. Morkoc, Electron. Lett. 19, 789 (1983).

- T. Drummond, R. J. Fisher, W. F. Kopp, and H. Morkoc, IEEE Trans. Electron Devices 30, 1806 (1983).

- 34) R. Fischer, T. J. Drummond, J. Klem, W. Kopp, T. S. Henderson, D. Perrachione, and H. Morkoc, IEEE Trans. Electron Devices 31, 1028 (1984)

- R. Yeats, D. C. D'Avanzo, K. Chan, N. Fernandez, T. W. Taylor, and C. Vogel, IEDM Tech. Dig., 1988, p. 842.

- 36) J. M. Dumas, F. Garat, and D. Lecrosnier, Electron. Lett. 23, 139 (1987).

- 37) M. Rocchi, Physica B+C 129, 119 (1985).

- W. Mickanin, P. Canfield, E. Finchem, and B. Odekirk, GaAs IC Symp. Tech. Dig., 1989, 211.6.

- 39) K. Asano, Y. Miyoshi, K. Ishikura, Y. Nashimoto, M. Kuzuhara, and M. Mizuta, Ext. Abstr. Solid State Devices and Materials (SSDM), 1998, p. 392.

- K. Asano, Y. Miyoshi, K. Ishikura, Y. Nashimoto, M. Kuzuhara, and M. Mizuta, IEDM Tech. Dig., 1998, p. 59.

- M. A. Khan, M. S. Shur, Q. C. Chen, and J. N. Kuznia, Electron. Lett. 30, 2175 (1994).

- W. Kruppa, S. C. Binari, and K. Doverspike, Electron. Lett. 31, 1951 (1995).

- S. C. Binari, W. Kruppa, H. B. Dietrich, G. Kelner, A. E. Wickenden, and J. A. Freitas, Jr., Solid-State Electron. 41, 1549 (1997).

- 44) P. B. Klein, J. A. Freitas, Jr., S. C. Binari, and A. E. Wickenden, Appl. Phys. Lett. 75, 4016 (1999).

- C. Nguyen, N. X. Nguyen, and D. E. Grider, Electron. Lett. 35, 1380 (1999)

- 46) R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, IEEE Trans. Electron Devices 48, 560 (2001).

- 47) B. M. Green, K. K. Chu, E. M. Chumbes, J. A. Smart, J. R. Shealy, and L. F. Eastman, IEEE Electron Device Lett. 21, 268 (2000).

- S. Arulkumaran, T. Egawa, H. Ishikawa, T. Jinbo, and Y. Sano, Appl. Phys. Lett. 84, 613 (2004).

- T. Hashizume, S. Ootomo, T. Inagaki, and H. Hasegawa, J. Vac. Sci. Technol. B 21, 1828 (2003).

- 50) B. Luo, J. W. Johnson, J. Kim, R. M. Mehandru, F. Ren, B. P. Gila, A. H. Onstine, C. R. Abernathy, S. J. Pearton, A. G. Baca, R. D. Briggs, R. J. Shul, C. Monier, and J. Han, Appl. Phys. Lett. 80, 1661 (2002).

- J. Hwang, W. J. Schaff, B. M. Green, H. Cha, and L. F. Eastman, Solid-State Electron. 48, 363 (2004).

- 52) Y. Ando, Y. Okamoto, H. Miyamoto, T. Nakayama, T. Inoue, and M. Kuzuhara, IEEE Electron Device Lett. 24, 289 (2003).

- 53) Y. Okamoto, Y. Ando, K. Hataya, T. Nakayama, H. Miyamoto, T. Inoue, M. Senda, K. Hirata, M. Kosaki, N. Shibata, and M. Kuzuhara, IEEE Trans. Microwave Theory Tech. 52, 2536 (2004).

- 54) H. Xing, Y. Dora, A. Chini, S. Heikman, S. Keller, and U. K. Mishra, IEEE Electron Device Lett. 25, 161 (2004).

- 55) W. Saito, T. Nitta, Y. Kakiuchi, Y. Saito, K. Tsuda, I. Omura, and M. Yamaguchi, IEEE Trans. Electron Devices 54, 1825 (2007).

- W. Saito, Y. Kakiuchi, T. Nitta, Y. Saito, T. Noda, H. Fujimoto, A. Yoshioka, T. Ohno, and M. Yamaguchi, IEEE Electron Device Lett. 31, 659 (2010).

- R. Chu, A. Corrion, M. Chen, R. Li, D. Wong, D. Zehnder, B. Hughes, and K. Boutros. IEEE Electron Device Lett. 32, 632 (2011).

- 58) M. T. Hasan, T. Asano, H. Tokuda, and M. Kuzuhara, IEEE Electron Device Lett. 34, 1379 (2013).

- 59) J. Joh and J. A. del Alamo, IEEE Trans. Electron Devices 58, 132 (2011).

- T. Sameshima, K. Sakamoto, Y. Tsunoda, and T. Saitoh, Jpn. J. Appl. Phys. 36, L687 (1997).

- 61) T. Sameshima and T. Saitoh, Jpn. J. Appl. Phys. 37, L1452 (1998).

- 62) P. Punchaipetch, M. Miyashita, Y. Uraoka, T. Fuyuki, T. Sameshima, and S. Horii, Jpn. J. Appl. Phys. 45, L120 (2006).

- 63) K. Yoshitsugu, T. Umemura, M. Horita, Y. Ishikawa, and Y. Uraoka, IEICE Tech. Rep. 113, 7 (2013) [in Japanese].

- 64) J. T. Asubar, Y. Kobayashi, K. Yoshitsugu, Z. Yatabe, H. Tokuda, M. Horita, Y. Uraoka, T. Hashizume, and M. Kuzuhara, IEEE Trans. Electron Devices 62, 2423 (2015).

- M. J. Hale, S. I. Yi, J. Z. Sexton, A. C. Kummel, and M. Passlack, J. Chem. Phys. 119, 6719 (2003).

- C. Hinkle, M. Milojevic, A. Sonnet, H. Kim, J. Kim, E. M. Vogel, and R. M. Wallace, ECS Trans. 19 [5], 387 (2009).

- 67) D. L. Winn, M. J. Hale, T. J. Grassman, J. Z. Sexton, A. C. Kummel, M. Passlack, and R. Droopad, J. Chem. Phys. 127, 134705 (2007).

- 68) M. Houssa, E. Chagarov, and A. Kummel, MRS Bull. 34, 504 (2009).

- D. J. Meyer, J. R. Flemish, and J. M. Redwing, Appl. Phys. Lett. 89, 223523 (2006).

- M. Tajima, J. Kotani, and T. Hashizume, Jpn. J. Appl. Phys. 48, 020203 (2009).

- 71) Y. Hori, Z. Yatabe, and T. Hashizume, J. Appl. Phys. 114, 244503 (2013).

- 72) J. T. Asubar, Y. Sakaida, S. Yoshida, Z. Yatabe, H. Tokuda, T. Hashizume, and M. Kuzuhara, Appl. Phys. Express 8, 111001 (2015).

- 73) L. Shen, R. Coffie, D. Buttari, S. Heikman, A. Chakraborty, A. Chini, S. Keller, S. P. DenBaars, and U. K. Mishra, IEEE Trans. Electron Devices 25, 7 (2004).

- 74) T. Kikkawa, Jpn. J. Appl. Phys. 44, 4896 (2005).

- 75) T. Kikkawa, M. Nagahara, N. Okamoto, Y. Tateno, Y. Yamaguchi, N. Hara, K. Joshin, and P. M. Asbeck, IEDM Tech. Dig., 2001, 25.4.1.

- 76) R. Coffie, D. Buttari, S. Heikman, S. Keller, A. Chini, L. Shen, and U. K. Mishra, IEEE Electron Device Lett. 23, 588 (2002).

- 77) W.-K. Wang, P.-C. Lin, C.-H. Lin, C.-K. Lin, Y.-J. Chan, G.-T. Chen, and J.-I. Chyi, IEEE Electron Device Lett. 26, 5 (2005).

- 78) J. T. Asubar, S. Yoshida, H. Tokuda, and M. Kuzuhara, Jpn. J. Appl. Phys. 55, 04EG07 (2016).

- 79) T. Tamura, J. Kotani, S. Kasai, and T. Hashizume, Appl. Phys. Express 1, 023001 (2008).

- K. Ohi, J. T. Asubar, K. Nishiguchi, and T. Hashizume, IEEE Trans. Electron Devices 60, 2997 (2013).

- 81) K. Ohi and T. Hashizume, Jpn. J. Appl. Phys. 48, 081002 (2009).

- 82) K. Ohi and T. Hashizume, Phys. Status Solidi B 9, 898 (2012).

- 83) J. T. Asubar, K. Nishiguchi, K. Ohi, and T. Hashizume, Phys. Status Solidi C 11, 857 (2014).

- 84) A. Suzuki, K. Akira, J. T. Asubar, H. Tokuda, and M. Kuzuhara, IEEE IMFEDK Tech. Dig., 2015, p. 36.

Masaaki Kuzuhara received his B.S., M.S., and Ph.D. degrees in electrical engineering from Kyoto University, Kyoto, Japan, in 1979, 1981, and 1991, respectively. He was a Visiting Researcher with the University of Illinois at Urbana-Champaign, IL, USA, from 1987 to 1988. He is currently a Professor with the Department of Electrical and Electronics Engineering, University of Fukui, Fukui, Japan, where he is focusing on physics and characterization of GaN-based heterojunction devices.

Joel T. Asubar received his M.S. and Ph.D. degrees from Nagaoka University of Technology, Niigata, Japan, working on ferromagnetic semiconductors. In 2010, he joined the Research Center for Integrated Quantum Electronics (RCIQE) of the Hokkaido University as a Post-doctoral fellow. Since 2014, he has been a Senior Assistant Professor with the University of Fukui, Fukui, Japan. His research interests include growth of heterojunctions and device physics of GaN-based transistors.

Hirokuni Tokuda received the Ph.D. degree in electronics engineering from the University of Tokyo, Tokyo, Japan, in 1978. He joined Murata Manufacturing Company, Ltd., Kyoto, Japan, in 2002, where he was the General Manager of the Department of Antenna Products. Since 2009, he has been with the University of Fukui, Fukui, Japan. His research interests include GaN-based HEMT devices and their physics.